designers and manufacturers of integrated circuit products with full inhouse capabilities for CAD/CAM, silicon process, testing, packaging and applications assistance.

# 1990 - 1991 IC DATA BOOK

GENNUM CORPORATION, P.O.Box 489, Station A, Burlington Ontario, Canada L7R 3Y3

Tel.(416) 632-2996 Fax:(416) 632-2055 Telex:061-8525

JAPAN BRANCH: 301 Aoba Building, 3-6-2 Takanawa, Minato-ku, Tokyo 108, Japan Tel.(03) 441-2096 Fax:(03) 448-8991

| Video and Broadcast Products     | 2 |

|----------------------------------|---|

|                                  |   |

| Power Supply Controllers         | 3 |

| Analog ASICs & IC Array Products | 4 |

|                                  |   |

| Hearing Instrument Products      | 5 |

About Gennum and its Products

# **CONTENTS**

| Sectio | n 1 - | About Gennum and its Products                                               |              |

|--------|-------|-----------------------------------------------------------------------------|--------------|

| page   | 1-5   | Contents                                                                    |              |

|        | 1-7   | Alphabetic and Numeric Listing of Products (and Device Order Numbers)       |              |

|        | 1-9   | Gennum Corporate Description                                                |              |

|        | 1-11  | Selling Policy                                                              |              |

|        | 1-13  | Available Packaging and Part Numbering                                      |              |

|        | 1-17  | Gennum Reliability Through Quality                                          |              |

| Sectio | n 2 - | Video and Broadcast Products                                                |              |

|        |       | data sheets                                                                 | ocument no.  |

| page   | 2-1   | GX401 Monolithic 1x1 Video Crosspoint Switch                                | 510-9-4      |

|        | 2-5   | GX411 Monolithic 1x1 Video Crosspoint Switch with 2 Latches                 | 510-56       |

|        | 2-9   | GX4201 Wideband, Monolithic 1x1 Video Crosspoint Switch                     | 510-74-3     |

|        | 2-15  | GX4301 Wideband, Monolithic 1x1 Video Crosspoint Switch                     | 510-94       |

|        | 2-19  | GY4102 Fast Toggling 2x1 Video Crosspoint Switch                            | 510-40-2     |

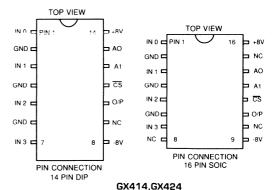

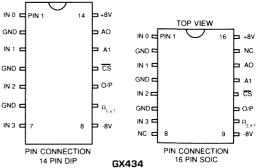

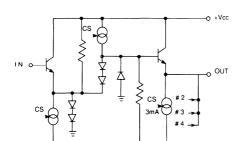

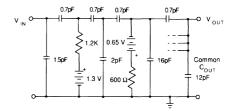

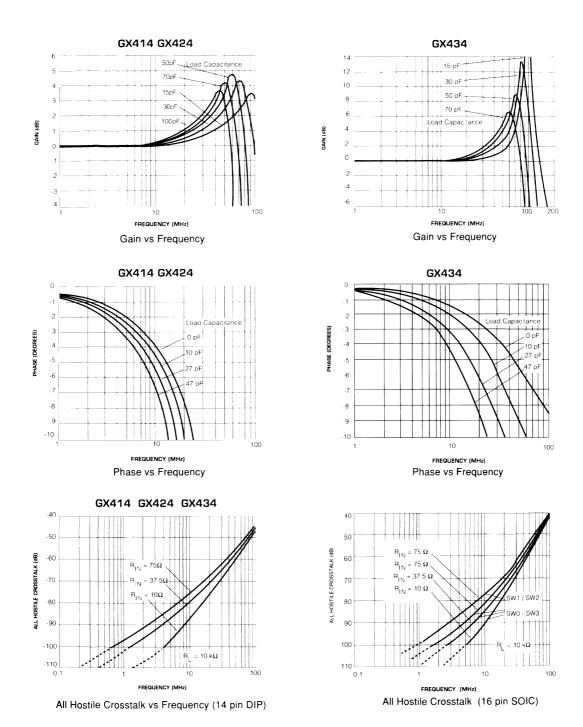

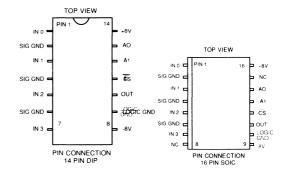

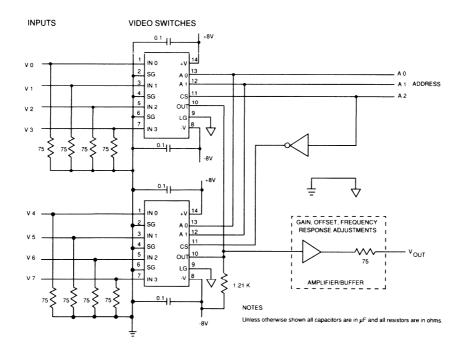

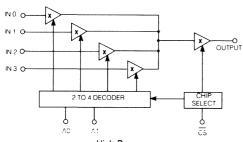

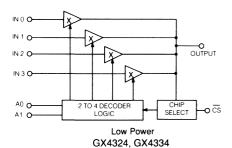

|        | 2-23  | GX414/424/434 Monolithic 4x1 Video Crosspoint Switches                      | 510-38-2     |

|        | 2-33  | GX414A Monolithic 4x1 Video Crosspoint Switch                               | 510-19-1     |

|        | 2-37  | GX214 Monolithic 4x1 CCTV Video Crosspoint Switch                           | 510-55-1     |

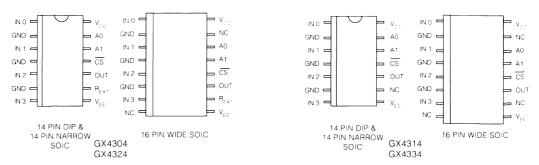

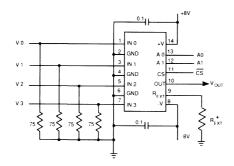

|        | 2-41  | GX4304/14/24/34 Wideband, Monolithic 4x1 Video Crosspoint Switch            | า 510-91     |

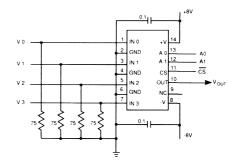

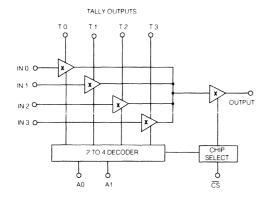

|        | 2-45  | GX4404/4414 Wideband, 4x1 Video Crosspoint Switch, with TALLY               | 510-90       |

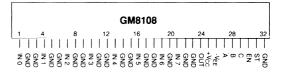

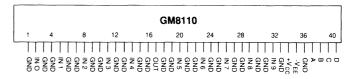

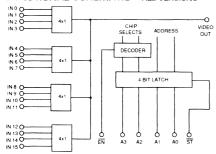

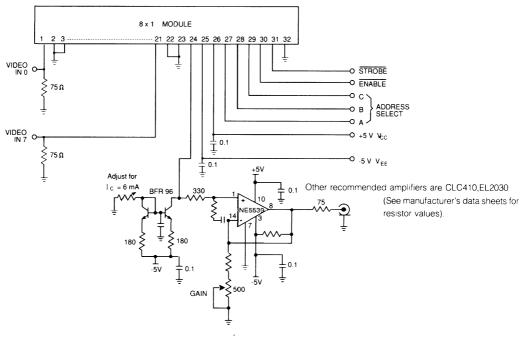

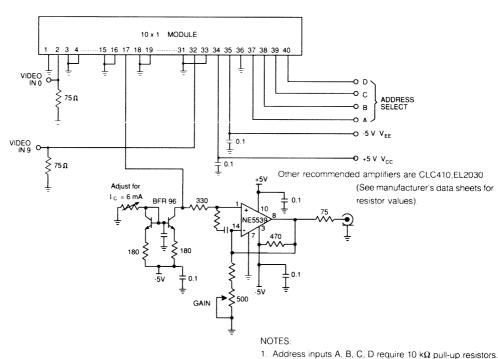

|        | 2-47  | GM8108/8110 HDTV, 8x1 & 10x1 Modular Video Multiplexers                     | 510-93       |

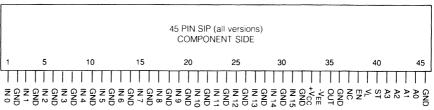

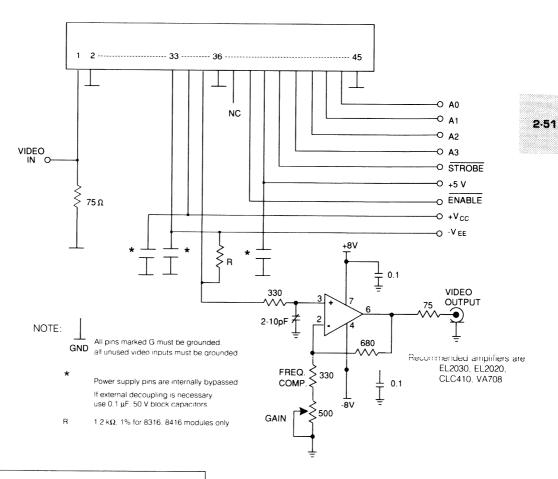

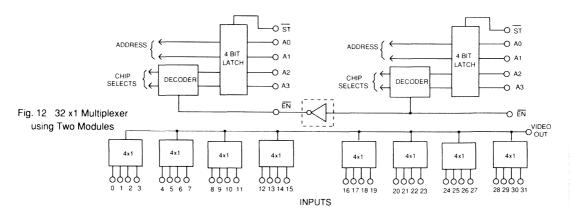

|        | 2-49  | GM8116/8216/8316, 16x1 Video Multiplexer Modules                            | 510-76-3     |

|        |       | application notes/application information                                   |              |

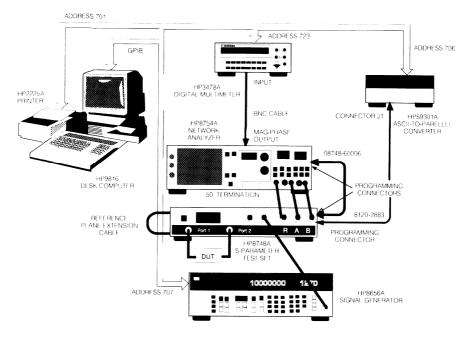

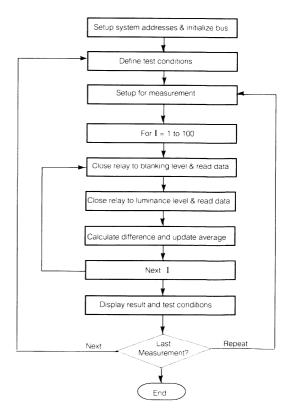

|        | 2-53  | Measuring Up to Broadcast (Differential Gain and Phase)                     | 510-14-1     |

|        | 2-57  | Virtually Glitch-free Bipolar Crosspoint Switches                           | 510-44       |

|        | 2-59  | Comparison of the 4x1 Video Crosspoint Switches                             | 510-45       |

|        | 2-61  | Comparison of the 16x1 Video Switching Multiplexers                         | 510-51-2     |

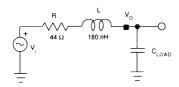

|        | 2-65  | Frequency Peaking Compensation of the GX414 and GX424                       | 510-39       |

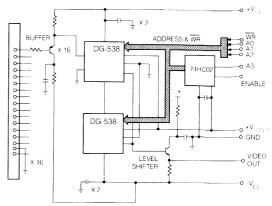

|        | 2-71  | 16x1 Video Crosspoint Evaluation Board                                      | 510-48       |

|        | 2-77  | Modelling and PSPICE <sup>5</sup> Analysis of 4x1 Video Crosspoint Switches | 510-65-1     |

|        | 2-81  | HDTV 8x1 and 10x1 Modular Multiplexers                                      | 510-84       |

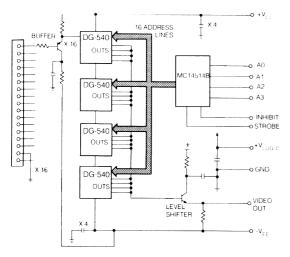

|        | 2-91  | Modular 16x1 Video Multiplexers                                             | 510-85       |

| Sectio | n 3 - | Power Supply Controllers                                                    |              |

|        |       | data sheets                                                                 | document no. |

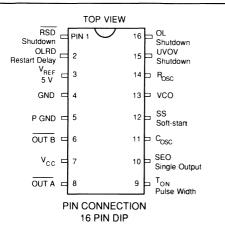

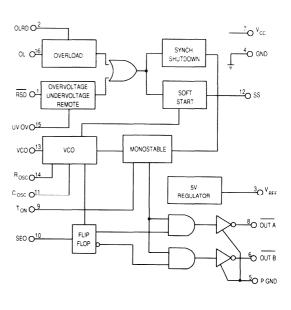

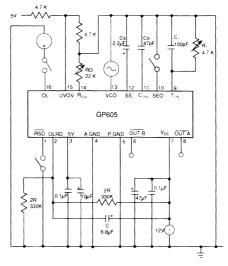

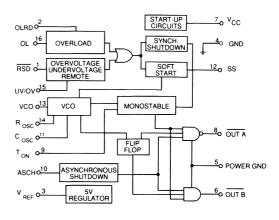

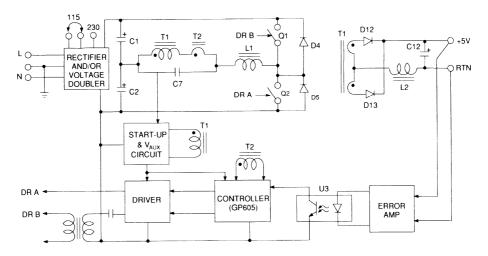

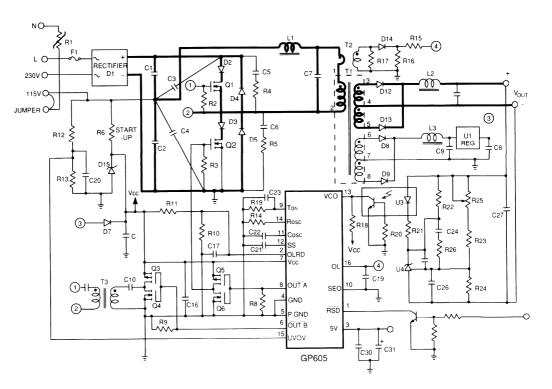

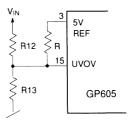

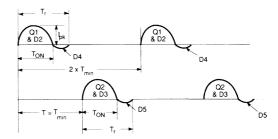

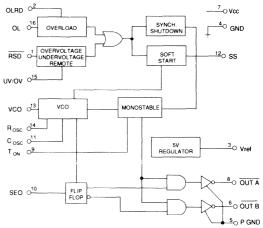

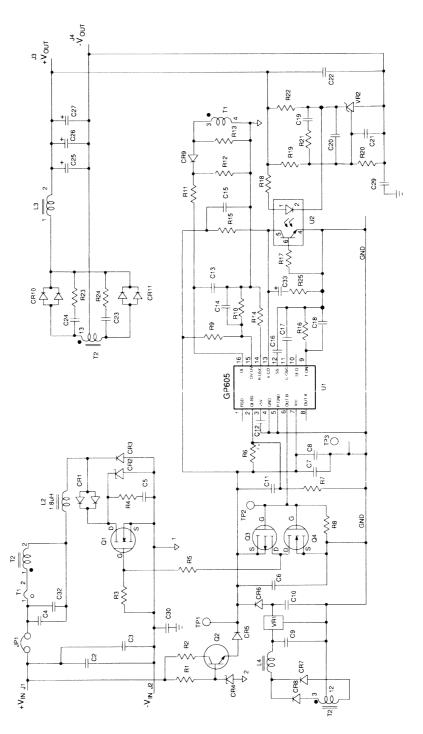

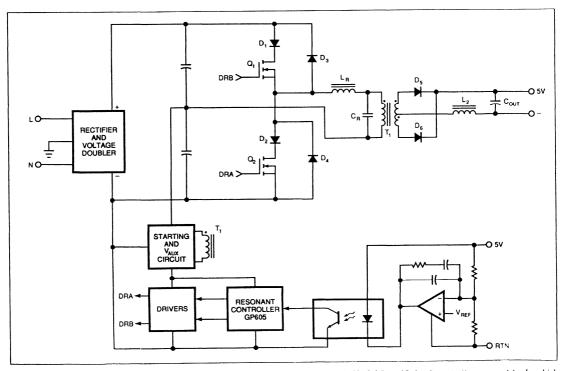

| page   | 3-1   | GP605 Resonant Mode Power Supply Controller                                 | 510-43-3     |

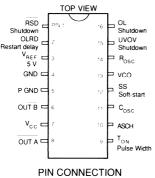

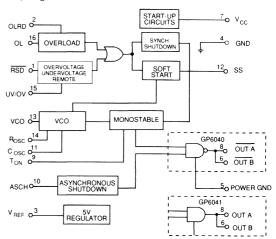

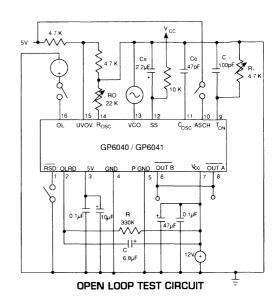

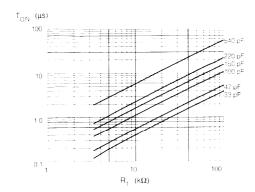

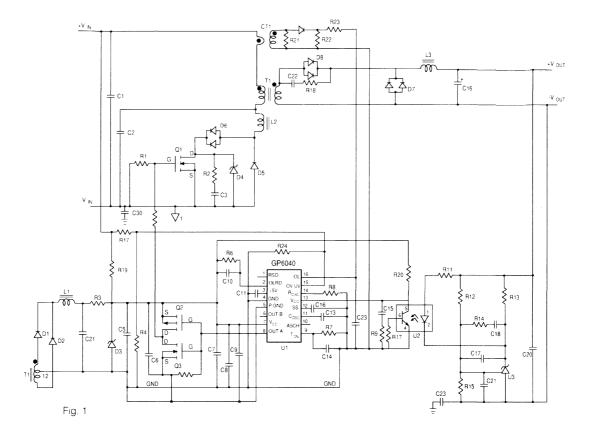

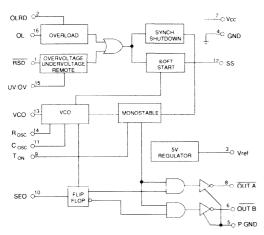

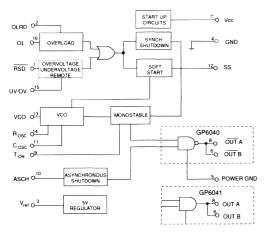

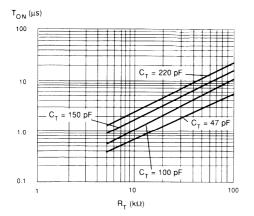

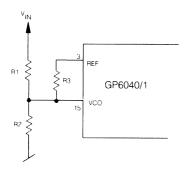

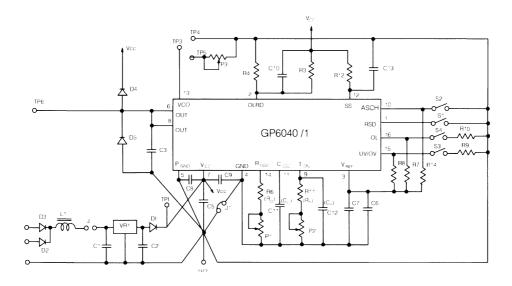

|        | 3-9   | GP6040/41 Single-ended Resonant Mode Controller                             | 510-59-4     |

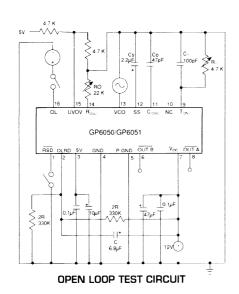

|        | 3-17  | GP6050/51 Push-pull Resonant Mode Controller                                | 510-58-2     |

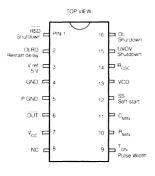

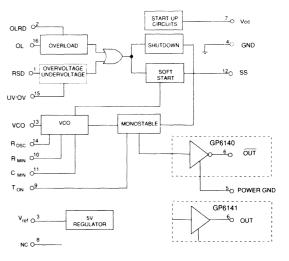

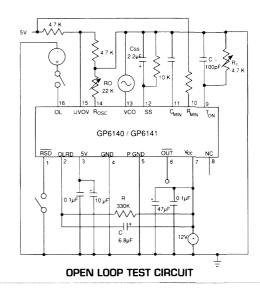

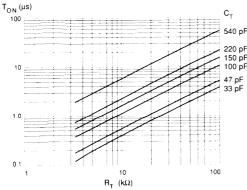

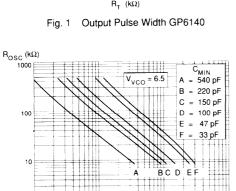

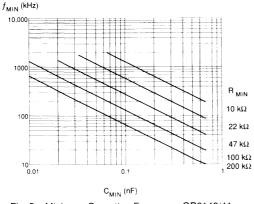

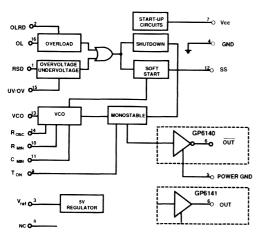

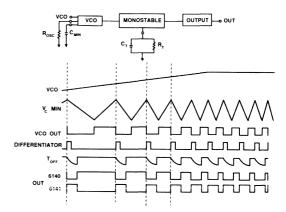

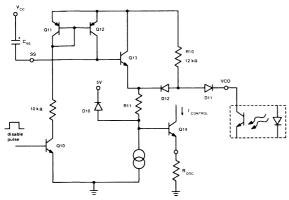

|        | 3-21  | GP6140/41 ZVS Single-ended Resonant Mode Controller                         | 510-97-1     |

|        | 3-27  | LD405 Resonant Mode Power Supply Controller                                 | 510-4-2      |

|        | 3-29  | GP2842 Current Mode PWM Controller                                          | 510-11-2     |

|        |       |                                                                             |              |

| Section | on 3 co |                                                            |                 |

|---------|---------|------------------------------------------------------------|-----------------|

|         |         | application notes/application information                  | document no.    |

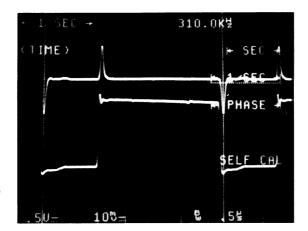

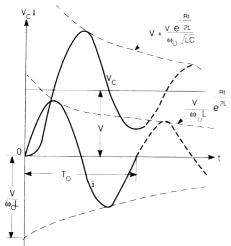

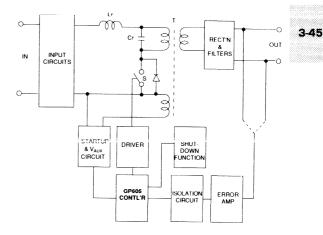

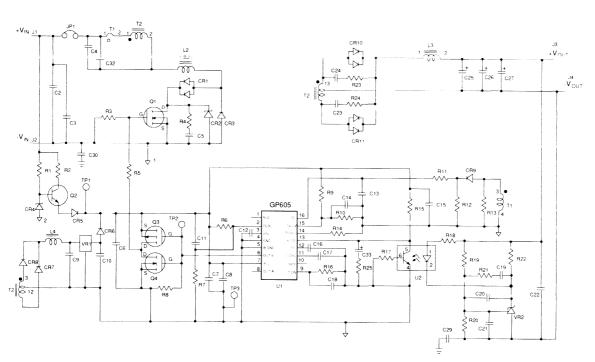

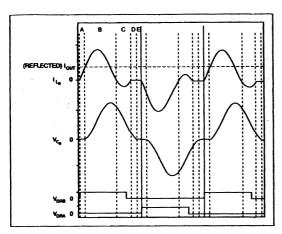

| page    | 3-33    | The GP605 in a Variable Frequency, Zero Current Switching, |                 |

|         |         | Half Bridge, Resonant Power Supply                         | 510-62-2        |

|         | 3-43    | The GP605 in a Variable Frequency, Zero Current Switching, |                 |

|         |         | Forward Mode, Resonant Power Supply                        | 510-63-2        |

|         | 3-55    | The GP6040 in 50W series Resonant Mode Power Supply        | 510-98-1        |

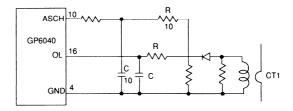

|         | 3-63    | Retrofitting the GP6040/1 into a GP605 Circuit             | 510-96          |

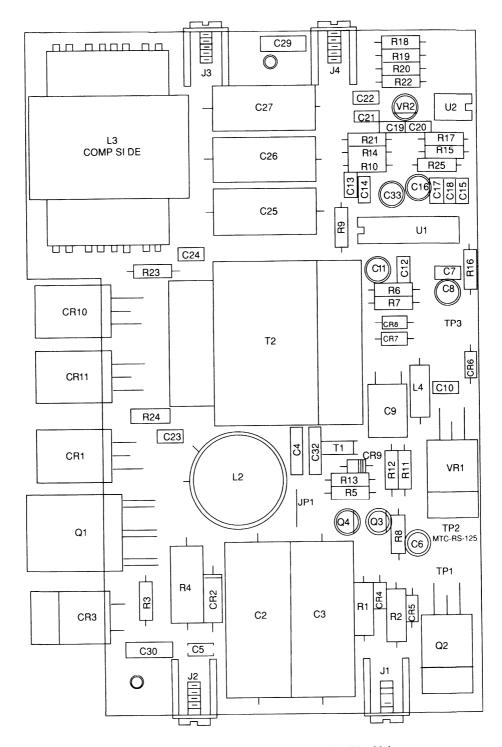

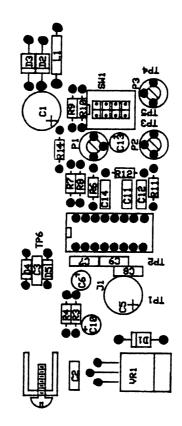

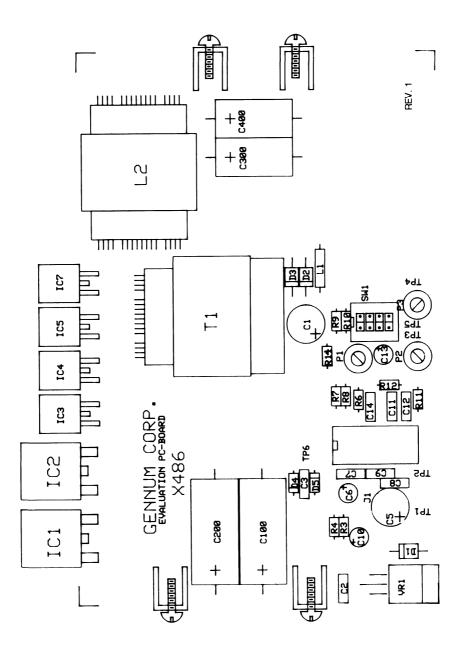

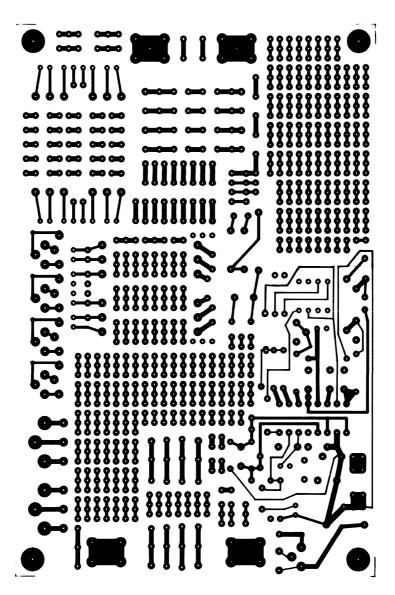

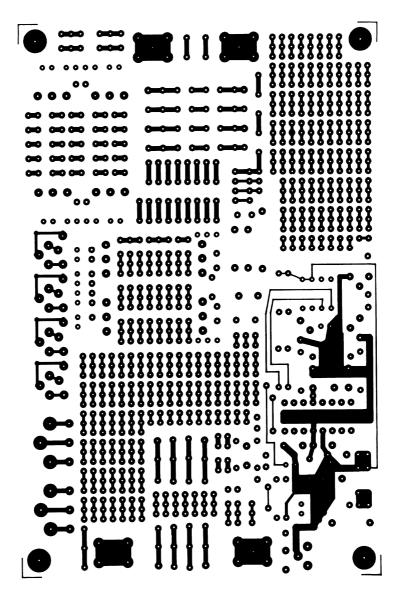

|         | 3-67    | X486 Evaluation PC Board Assembly Manual                   | 510-68          |

|         | 3-75    | X485 DC-DC Converter Kit                                   | 510-42          |

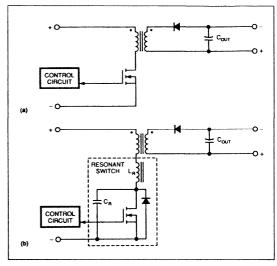

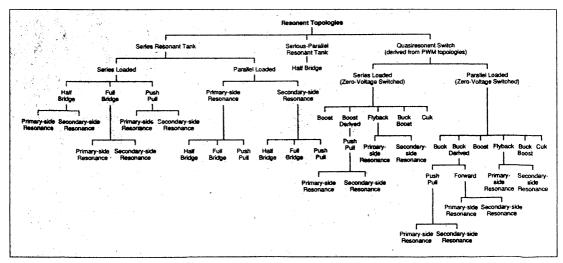

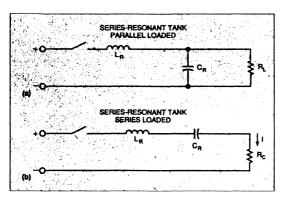

|         | 3-77    | Resonant Mode Design Techniques EDN reprint Nov.'89        | 600-13          |

|         | 3-89    | New High Performance ZVS Resonant Mode Controller          |                 |

|         |         | HFPC Conference paper reprint Apr.'90                      | 600-14          |

| Secti   | on 4 -  | - Analog ASICs & IC Array Products                         |                 |

|         |         | data sheets                                                | document no.    |

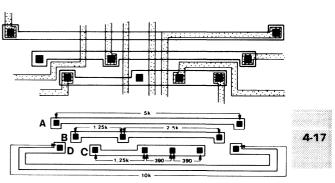

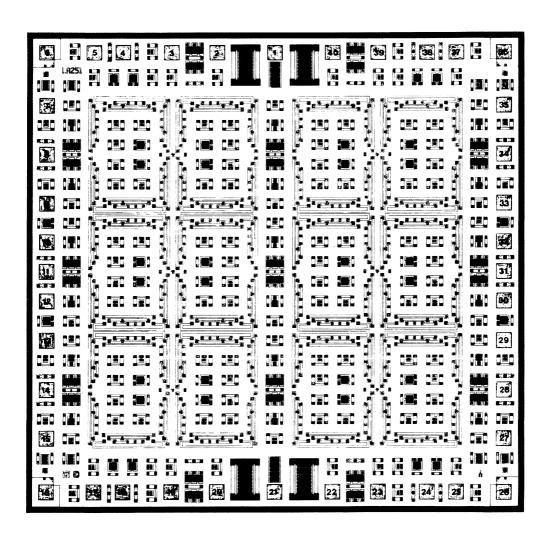

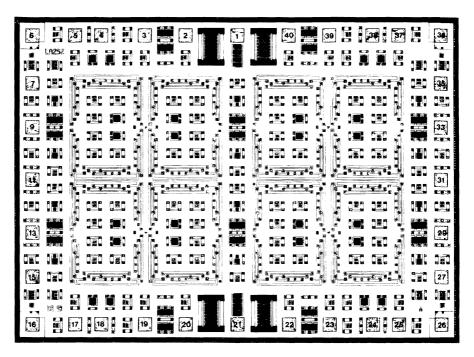

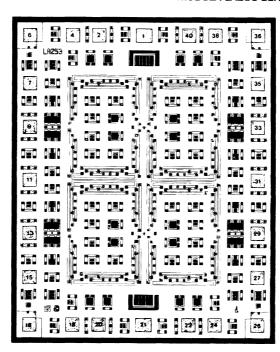

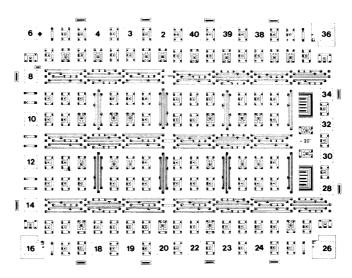

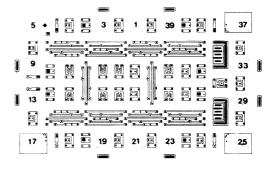

| page    | 4-1     | LA200 & THE LA250 Series Linear Arrays                     | 500-67-4        |

|         | 4-23    | GA911 RF Analog Tile -based Linear Array                   | 510-95-1        |

| Secti   | on 5 ·  | - Hearing Instrument Products                              |                 |

|         |         | shortform listing                                          |                 |

| page    | 5-1     | Shortform catalog product listing (BR522) includes:        |                 |

|         |         | Low Voltage (1.0 V)                                        | data sheets     |

|         |         | class A amplifiers                                         | and application |

|         |         | class A compression amplifiers                             | notes supplied  |

|         |         | class A peak clipping amplifers                            | on request      |

|         |         | class B amplifiers                                         |                 |

|         |         | preamplifiers                                              |                 |

|         |         | programmable series                                        |                 |

|         |         | transconductance blocks                                    |                 |

|         |         | filters                                                    |                 |

|         |         |                                                            |                 |

# ALPHABETICAL AND NUMERICAL LISTING OF GENNUM PRODUCTS

### AND DEVICE ORDER NUMBERS

| DEVICE NO.       | PAGE NO | . DESCRIP                                | TION                      | ORDER NO.                      | DOCUMENT NO |

|------------------|---------|------------------------------------------|---------------------------|--------------------------------|-------------|

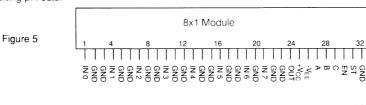

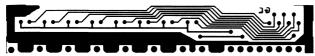

| GM8108<br>GM8110 | 2-47    | 8x1 HDTV Mux.                            | 32 pin SIP                | GM8108 - CSG                   | 510-93      |

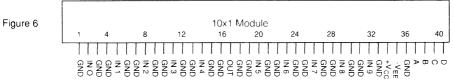

| GIMOTTO          |         | 10x1 HDTV Mux.                           | 40 pin SIP                | GM8110 - CSH                   |             |

| GM8116           | 2-49    | 16x1 Mux. 48                             | 5 pin SOIC wide           | GM8116 - CSK                   | 510-76      |

| GM8216           |         |                                          | oin SOIC narrow           | GM8216 - CSK                   | 3.373       |

| GM8316           |         | 16x1 CCTV Mux. 45                        | 5 pin SOIC wide           | GM8316 - CSK                   |             |

| GM8416           |         |                                          | oin SOIC narrow           | GM8416 - CSK                   |             |

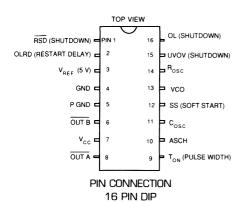

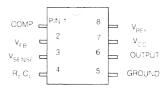

| GP2842           | 3-29    | Current Mode PWM Controlle               | r 16 pin DIP              | GP2842 - ID -                  | 510-11      |

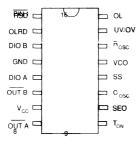

| GP6040           | 3-9     | Single-ended RM Controller               | 16 pin DIP                | GP6040 - CDC                   | 510-59      |

|                  |         |                                          | 16 pin SOIC               | GP6040 - CKC                   | 010 03      |

| GP6041           | 3-9     | Single-ended RM Controller               | 16 pin DIP                | GP6041 - CDC                   | E 10 E 0    |

|                  |         | g = = ================================   | 16 pin SOIC               | GP6041 - CKC                   | 510-59      |

| GP605            | 3-1     | RM Power Supply Controller               | 16 pin DIP                | GP605 CDC                      | 540.40      |

|                  |         | 2 Gappiy Gontioner                       | 16 pin SOIC               | GP605 CDC<br>GP605 CKC         | 510-43      |

|                  |         |                                          | 16 pin DIP                |                                |             |

|                  |         |                                          |                           | GP605 IDC                      |             |

|                  |         |                                          | 16 pin SOIC               | GP605 IKC                      |             |

| GP6050           | 3-17    | Push-pull RM Controller                  | 16 pin DIP                | GP6050 - CDC                   | 510-58      |

|                  |         |                                          | 16 pin SOIC               | GP6050 - CKC                   |             |

| GP6051           |         |                                          | 16 pin DIP                | GP6051 - CDC                   | 510-58      |

|                  |         |                                          | 16 pin SOIC               | GP6051 - CKC                   |             |

|                  |         |                                          |                           |                                |             |

| GP6140           | 3-21    | ZVS Single-ended RM Contr.               | 16 pin DIP                | GP6140 - CDC                   | 510-97      |

|                  |         |                                          | 16 pin SOIC               | GP6140 - CKC                   |             |

|                  |         |                                          | 16 pin DIP                | GP6140 - EDC                   |             |

|                  |         |                                          | 16 pin SOIC               | GP6140 - EKC                   |             |

| •                |         |                                          | 16 pin SOIC               | GP6140 - MDC                   |             |

| GP6141           | 3-21    | ZVS Single-ended RM Contr.               | 16 pin DIP                | GP6141 – CDC                   | 510-97      |

|                  |         | •                                        | 16 pin SOIC               | GP6141 – CKC                   | 310-31      |

|                  |         |                                          | 16 pin DIP                | GP6141 – EDC                   |             |

|                  |         |                                          | 16 pin SOIC               | GP6141 - EKC                   |             |

|                  |         |                                          | 16 pin SOIC               | GP6141 - MDC                   |             |

| GX214            | 2-37    | 4x1 Crosspoint Switch                    | 14 pin DIP                | GX214 CDB                      | E10 FF      |

|                  | _ 2,    | C. C | 14 pin SOIC               | GX214 CKB                      | 510-55      |

|                  |         |                                          | 16 pin SOIC               | GX214 CKC                      |             |

| GX401            | 2-1     | 1x1 Crosspoint Switch                    | ohin                      | CV401 CC                       | 540.0.0     |

|                  | _ '     | TAT Grosspoint Switch                    | chip<br>7 pin SIP         | GX401 CC -<br>GX401 CSN        | 510-9-3     |

| GX411            | 2-5     | 1x1 Crosspoint Switch, dual la           |                           | GX411 CSA                      | 510-56      |

| GX414            |         |                                          |                           |                                |             |

| G/114            | 2-23    | 4x1 Crosspoint Switch                    | chip                      | GX414 CC -                     | 510-38      |

|                  |         |                                          | 14 pin DIP<br>16 pin SOIC | GX414 – – CDB<br>GX414 – – CKC |             |

| 074444           | 0.00    |                                          |                           | GMT14 UNC                      |             |

| GX414A           | 2-33    | 4x1 Crosspoint Switch                    | 14 pin DIP                | GX414 - ACDB                   | 510-19      |

|                  |         |                                          | 16 pin SOIC               | GX414 - ACKC                   |             |

| DEVICE NO. | PAGE NO.                                                                                                                              | DESCRIPTIO                              | ONN                                         | ORDER NO.                                    | DOCUMENT NO. |  |  |  |

|------------|---------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------|---------------------------------------------|----------------------------------------------|--------------|--|--|--|

|            |                                                                                                                                       |                                         |                                             |                                              |              |  |  |  |

| GX4201     | 2-9                                                                                                                                   | 4x1 Wideband Xpt Sw.(Tally)             | 8 pin DIP<br>8 pin SOIC                     | GX4201 - CDA<br>GX4201 - CKA                 | 510-74       |  |  |  |

| GX424      | 2-23                                                                                                                                  | 4x1 Crosspoint Switch                   | 14 pin DIP<br>16 pin SOIC                   | GX424 CDB<br>GX424 CKC                       | 510-38       |  |  |  |

| GX4301     | 2-15                                                                                                                                  | 1x1 Wideband Crosspoint Sw.             | 8 pin SOIC<br>8 pin SIP                     | GX4301 - CKA<br>GX4301 - CSA                 | 510-94       |  |  |  |

| GX4304     | 2-41                                                                                                                                  | 4x1 Wideband Crosspoint Sw.             | 14 pin DIP<br>14 pin SOIC<br>16 pin SOIC    | GX4304 - CDB<br>GX4304 - CKB<br>GX4304 - CKC | 510-91       |  |  |  |

| GX4314     | 2-41                                                                                                                                  | 4x1 Wideband Crosspoint Sw.             | 14 pin DIP<br>14 pin SOIC<br>16 pin SOIC    | GX4314 - CDB<br>GX4314 - CKB<br>GX4314 - CKC | 510-91       |  |  |  |

| GX4324     | 2-41                                                                                                                                  | 4x1 Wideband Crosspoint Sw.             | 14 pin DIP<br>14 pin SOIC<br>16 pin SOIC    | GX4324 - CDB<br>GX4324 - CKB<br>GX4324 - CKC | 510-91       |  |  |  |

| GX4334     | 2-41                                                                                                                                  | 4x1 Wideband Crosspoint Sw.             | 14 pin DIP<br>14 pin SOIC<br>16 pin SOIC    | GX4334 - CDB<br>GX4334 - CKB<br>GX4334 - CKC | 510-91       |  |  |  |

| GX434      | 2-23                                                                                                                                  | 4x1 Crosspoint Switch                   | 14pin DIP<br>16 pin SOIC                    | GX434 CDB<br>GX434 CKC                       | 510-38       |  |  |  |

| GX4404     | 2-45                                                                                                                                  | 4x1 Wideband Xpt Sw. (Tally)            | 16 pin DIP<br>16 pin SOIC                   | GX4404 - CDC<br>GX4404 - CKD                 | 510-90       |  |  |  |

| GX4414     | 2-45                                                                                                                                  | 4x1 Wideband Xpt Sw. (Tally)            | 16 pin DIP<br>16 pin SOIC                   | GX4414 - CDC<br>GX4414 - CKD                 | 510-90       |  |  |  |

| GY4102     | 2-19                                                                                                                                  | Fast Toggling Crosspoint Sw.            | 8 pin DIP<br>8 pin SOIC                     | GY4102 – CDA<br>GY4102 – CKA                 | 510-40       |  |  |  |

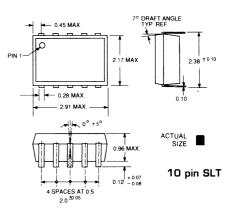

|            | All above devices order (part) no.s must consist of a combination of 10 components, (letters, numbers or spaces). See also page 1-16. |                                         |                                             |                                              |              |  |  |  |

| LD405      | 3-27                                                                                                                                  | RM Power Supply Controller For replacem | 16 pin DIP<br>16 pin SOIC<br>ent parts only | LD405D<br>LD405K                             | 510-4        |  |  |  |

Fraser Drive Headquarters Building in Burlington, Ontario, which houses Gennum's business offices, R&D, Marketing, Masking, Test and Assembly areas.

The Landmark Road facility, also in Burlington, Ontario, where all the silicon processes are located.

Gennum Corporation supplies electronic components to manufacturers of electronic systems all over the world. Our business is the design, manufacture and marketing of silicon integrated circuits, (ICs). Employing over 200 people, Gennum is housed in two modern facilities in Burlington, Ontario, just a few miles west of Toronto. A recent addition is the opening of an office in Tokyo, Japan. To better serve our worldwide customers Gennum has 31 agents and/or design centres in 14 countries.

Gennum Corporation, created in 1987, continues the integrated circuit operations, conducted since 1973, by LTI, Gennum's parent company. This business which Gennum Corporation continues has grown to more than seventeen million dollars of sales in 1989, sharing in the tremendous growth which has been experienced in electronic component manufacturing since 1973.

Gennum's continued growth has occurred because of a business philosophy: - attention to individuals' needs; customers, suppliers, employees and investors alike.

Capabilities in terms of human and physical resources extend through all facets of the company. These include technology development, new product design and development, and all aspects of wafer fabrication, device assembly and testing. Skills and abilities are constantly improved through the application of the latest tools and technologies applied to new products and existing products alike. This gives Gennum customers the competitive advantage essential to their success.

Currently Gennum Corporation serves five distinct areas within the electronic systems and subsystems market.

- resonant mode controller ICs for power supplies.

- crosspoint switches for the video/broadcast industry

- special application products

- semicustom IC linear arrays

- low voltage, low current hearing instrument products such as amplifiers and filters.

This comprehensive catalog provides detailed information on products in all five areas, with data sheets, application notes, and packaging information. Applications assistance is available at any time from our applications engineers.

## Corporate Mission:

Excellence Through People and Technology!

- serve the customer

- respect people

- pursue excellence

The exacting processes of integrated circuit design and production force a hard discipline on those who manufacture them and Gennum Corporation is no exception to this rule.

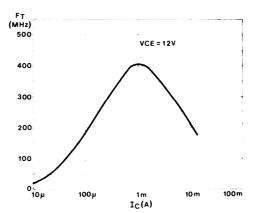

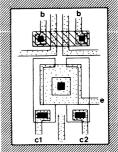

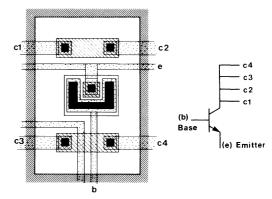

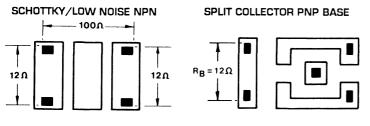

The company's silicon processing includes linear bipolar circuits with operating ranges from as low as 1.0V up to 30V, transistor current handling capability up to 3A, and 2.5 GHz  $f_{\rm T}$  transistors. In combination with the above, ion implanted JFETs and Schottky diodes can be added. A recent addition to our capabilities is CMOS technology.

To help us stay in the forefront of technology, Gennum maintains affiliations with the scientific and engineering departments of five Canadian universities.

Computer aided design is a major component of our product development cycle. The highly efficient equipment and personnel are able to shorten design time and cost while increasing reliability. Simulation programs such as SPICE, SUPREM and COMPACT are available in-house for design optimization. Their use allows investigation of circuit performance under the most extreme cases of device matching and over as wide a range of temperature as necessary.

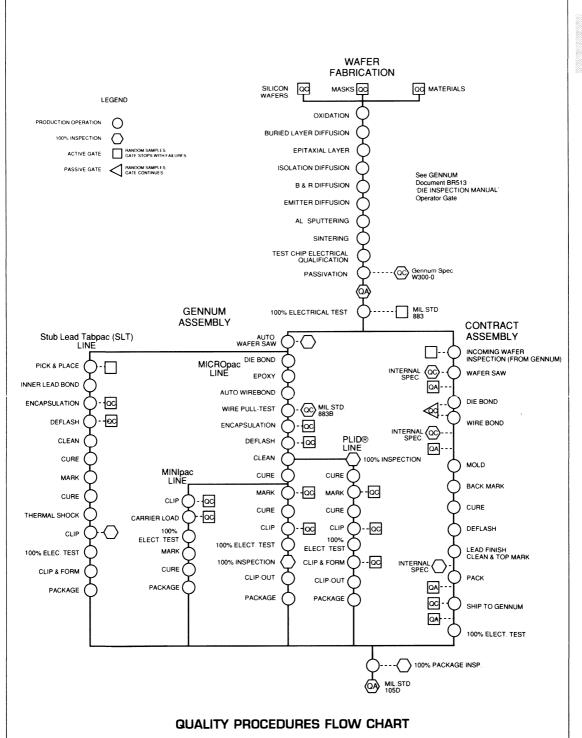

To ensure that every product meets Gennum's high quality standards, we perform in-line sample inspection on each batch from incoming inspection, to the final test of the finished product. Gennum's entire manufacturing process is governed by strict production controls performed by production personnel, as well as quality control audit inspections to double check the quality practices instituted by other groups.

## **SELLING POLICY**

GENNUM

**GENNUM 010**

1-11

#### 1. Order Acceptance

No order is contractually binding on Gennum Corporation unless accepted in writing by an authorized representative of the Company. All orders are accepted in accordance with the terms outlined herein notwithstanding any conflicting terms which may appear on the Buyer's order.

Orders will be accepted for:

- 1.1 Complete delivery in a single shipment on a specific date. These are called Single Shipment Orders.

- 1.2 Delivery in many shipments spread over an extended period. These are called Extended Period Blanket (EPB) Orders.

#### 2. Contractual Period

- 2.1 A purchase order which has been accepted in accordance with Paragraph 1 above, will be contractually binding on both Seller and Buyer for the contractual period, which lasts from the date of first shipment to the date on which the total quantity of units ordered has been shipped by the Seller or for twelve months, whichever comes first.

- 2.2 The contractual period may be extended beyond the twelve month limit provided both Buyer and Seller agree so to do in writing.

#### 3. Prices

Prices shown on a quotation will remain firm for the validity period of the quotation. Prices shown on an order acknow-legement will remain firm during the contractual period, except that a price decrease which is freely offered by the Seller will apply to all shipments made after its effective date.

#### 4. Termination of an Order

An order shall be automatically terminated at the end of the contractual period. The Buyer may terminate an order prematurely by providing the Seller with 60 days notice in writing. In the event of premature termination the following shall apply.

4.1 The Seller is entitled to ship all parts which were previously scheduled for shipment before termination date by the Buyer.

and

4.2 The Buyer is liable for payment for all parts shipped in accordance with Paragraph 4.1 above, including additional payments arising from increased per unit prices at the reduced quantity. The Buyer is liable for back billing for all parts shipped at the applicable blanket order prices.

and

4.3 Payment of a reasonable charge based upon expenses incurred and commitments made in the execution of the purchase contract by Gennum Corporation up to the date of receipt of the notice of termination; the charge being a minimum of 15% of the unrealized invoice value of the order.

#### 5. Extended Period Blanket (EPB) Orders

- 5.1 EPB Orders will be accepted for any products in quantities to cover expected requirements over the contractual period. The total of all products ordered may be used to determine the per unit price of each proprietary product accordance with the quotation submitted by the Seller to the Buyer.

- 5.2 Changes to EPB orders by the Buyer, including changes in device types ordered, and changes in order quantity, either decrease or increase, will be accepted by the Seller subject to the following limitations:

- 5.2.1 Within 3 months from date of order acceptance, a change in total quantity ordered, either an increase or decrease, which results in the total number of units being in a different price/quantity range, will automatically change the per unit price for all prior and subsequent shipments.

- 5.2.2 At any time after order acceptance, changes in device types ordered, either by addition, deletion, or substitution, shall at the discretion of the Seller, require sixty days notice in writing.

#### 6. Shipping Schedule

Unless purchase orders are accompanied by a shipping schedule, shipment will be at the Seller's discretion. In the case of Extended Period Blanket Orders, the order must be accompanied by a shipping schedule which releases at least 40% of the total order quantity for shipment in a period not to exceed five months from the beginning of the contractual period. The remaining parts on a EPB order may be released at the Buyer's discretion provided:

- 6.1 All parts are scheduled for **shipment** within the Contractual Period. and

- 6.2 The Buyer provides the Seller with at least 12 weeks notice of any new shipping requirement or amendment to existing shipping schedule.

#### 7. Terms of Payment

The terms of payment agreed between the Seller and Buyer will be clearly shown on the Order Acceptance document supplied by the Seller to the Buyer. Until credit terms have been negotiated, the only terms of payment which will be accepted by the Seller are cash with order. Gennum Corporation reserves the right to apply a monthly service charge not in excess of two percent per month, on the overdue payment balance, provided it supplies the Buyer with thirty days notice in writing.

#### 8. Loss or Damage in Transit or Short Shipment

All shipments should be inspected by the Buyer immediately upon receipt. If there is evidence of loss or damage during transit, the Buyer should immediately file a claim with the carrier. Gennum Corporation will cooperate with the Buyer to ensure that a proper adjustment with the carrier is obtained. In the event of short shipment, claims must be made directly to Gennum Corporation in writing within fifteen working days after receipt of goods.

#### 9. Warranty

Gennum Corporation warrants that its products will be free of defects in material and workmanship and will perform as specified in the governing data sheet for one year from date of shipment. The liability of Gennum Corporation is limited to repairing, replacing F.O.B. Burlington, Ontario, Canada, products which are returned by the Purchaser at **his expense** during the warranty period. Final determination as to whether a product is actually defective rests with Gennum Corporation. This warranty shall automatically become null and void if the products are used in an unreasonable manner or in a manner which exceeds the absolute maximum ratings specified by the governing data sheet.

- 9.1 Returns Warranty

- An RMO number and authorization must be obtained from Gennum Corporation before material is returned.

- 9.1.1 If an entire shipment is being returned based on a Quality Assurance Sampling Process, the defective devices must first be sent to Gennum Corporation for confirmation. Once confirmed, the entire shipment may be returned, following normal procedures. Devices which have been used or subjected to any production process are not eligible for credit.

- 9.2 Non-Warranty

Any product returned for reasons other than defective must receive an RMO number and authorization and will be subject to a restocking charge.

#### 10. Limitation of Liability

Notwithstanding any other provision in this contract or any applicable statutory provisions, neither Gennum Corporation nor the purchaser shall be liable to the other for special or consequential damages or damages for loss of use arising directly or indirectly from any breach of this contract (fundamental or otherwise) or from any tortius acts or omissions of their respective employees or agents and in no event shall the liability of Gennum Corporation exceed the unit price of the product.

#### 11. Force Majeure

Gennum Corporation shall not be responsible or liable for any loss, damage, detention or delay caused by war, invasion, insurrection riot, the order of any civil or military authority, or by fire, flood, weather or other acts of the elements, breakdown, lockouts, strikes or labour disputes, the failure of its suppliers to meet their contractual obligations, or, without limitation of the foregoing, any other cause beyond its reasonable control and the receiving of the product by the Purchaser shall constitute a waiver of all claims for loss or damage due to delay.

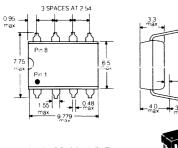

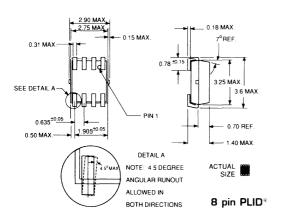

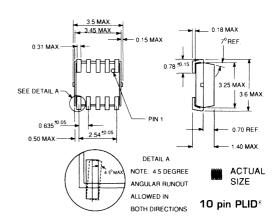

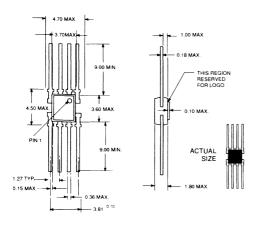

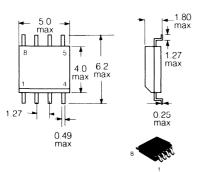

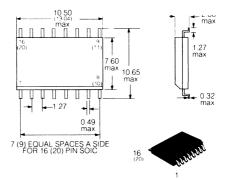

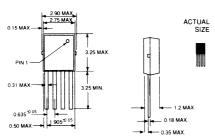

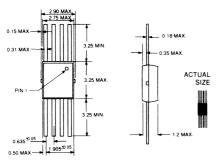

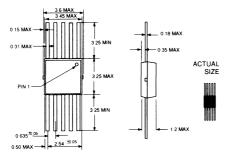

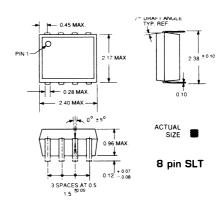

### AVAILABLE PACKAGING & PART NUMBERING (see page 1-16)

Gennum can provide a wide variety of proprietary and standard packages.

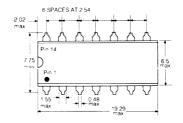

8 pin Molded DIP

14 pin Molded DIP

Other standard DIP packaging is available for custom and semicustom products.

#### **DIP PACKAGES**

All dimensions in millimetres

##

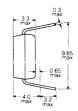

#### OTHER STANDARD PACKAGING

All dimensions in millimetres

#### **GENNUM PROPRIETARY PACKAGING**

All dimensions in millimetres

8 pin MINIpac

10 pin MINIpac

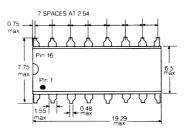

8 pin Molded SOIC

16 and 20 pin Molded SOIC

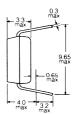

#### GENNUM PROPRIETARY PACKAGING continued

All dimensions in millimetres

4 pin MICROpac

8 pin MICROpac

10 pin MICROpac

### GENNUM PROPRIETARY PRODUCTS PART NUMBERING SYSTEM

#### **PACKAGES**

| CC                         | Chip                                             |      | DA DB DC DE DF DG DH DI DJ DK DL | 8 0.3<br>14 0.3<br>16 0.3<br>18 0.3<br>20 0.3<br>22 0.4<br>24 0.3<br>24 0.6<br>28 0.3<br>28 0.6<br>40 0.6 | plas     |      | DIP | EA<br>EB<br>EC<br>EE<br>EF       | 8 0.3<br>14 0.3<br>16 0.3<br>18 0.3<br>22 0.4 | ceramic        | DIP         |

|----------------------------|--------------------------------------------------|------|----------------------------------|-----------------------------------------------------------------------------------------------------------|----------|------|-----|----------------------------------|-----------------------------------------------|----------------|-------------|

| KA<br>KB<br>KC<br>KD<br>KF | 8 0.15<br>14 0.15<br>16 0.3<br>18 0.15<br>22 0.4 | SOIC |                                  | PJ<br>PM                                                                                                  | 28<br>44 | PLCC |     | SA<br>SF<br>SG<br>SH<br>SK<br>SN | 20<br>32<br>40                                | 11<br>11<br>12 | MODULES<br> |

For product order number designations see pages 1-6 and 1-7

Wafer Inspection

Automated Wafer Probe

# RELIABILITY THROUGH QUALITY ————

- Procedures designed to meet MIL.STD.105D

- Quality audits

- All employees participate in the "Quality Improvement Process"

- Products are sampled for reliability at all stages of manufacture.

Automated Test Equipment and DIP Handler

Wire Pull Test

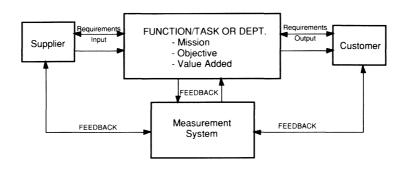

#### QUALITY IMPROVEMENT JOURNEY

Quality is important in any industry but even more so in a high-tech environment. Companies such as Gennum, that market on a global scale must pursue quality relentlessly.

This commitment to quality commenced in earnest in the mid 1980's with intensive quality training for all Gennum employees. The quality focus is on employee participation and interaction. Therefore you'll find quality circles, or teams, or task forces operating in design, marketing, manufacturing, administration, human resources and building services. Performance indicators and goals are defined and monitored constantly, and variances are analyzed. The precepts of quality are threefold:

In all activities

- know the job requirements.

- set standards to meet requirements,

- conform to standards.

Gennum's quality improvement results are known and respected by our customers, more than half of whom do not perform any incoming inspection of our products. Our average outgoing quality (AOQ) defects level has been halved in each of the last six years, a visible result of a quality program that works. Our vision of quality effectiveness is achieving a goal of zero defects.

Gennum's products are sold in 20 countries on five continents. With this wide customer base and a broad spectrum of products, customer satisfaction is of vital importance. It has been said that quality means — measure, measure, and measure. This is especially true for measurement of customer satisfaction. Since the late 1980's this has been incorporated in the business plans of the marketing groups. We are proud that our customer's rating of their satisfaction

with Gennum is consistantly above industry average.

#### THE PEOPLE

Gennum employees are the cornerstone of our quality processes. As part of the quality training, employees learn that: knowlege + practice + feedback = success. This is an integral part of the quality process at Gennum and is followed by the application of that training in all aspects of the job. Finally the measurement feedback assures that quality is an ongoing improvement journey.

At Gennum the emphasis is on prevention of error, rather than the analysis of failure. With this in mind, Gennum's Quality Assurance department fulfills the function of auditing the quality of processes, products, systems and procedures, at the same time endeavouring to instill in each employee an awareness to be their own quality control inspector. Of course Q.C. stations do exist throughout the production and design areas, however, the ultimate responsibility rests with each employee within each process. Prevention of error is, of course, much more cost-effective than appraisal. Therefore the Quality Assurance group is only a final "gate" in the path to customer satisfaction.

#### THE TOOLS

Gennum's philosophy states that each employee is responsible for quality and quality improvement. Therefore, tools for day-to-day work activities are an important resource to attain quality and excellence. These range from powerful networked PC's and work-stations, to state-of-the-art computer aided design (CAD) facilities. The administrative data processing runs a full "MRP II" program with capabilities to attain class A operation.

In the last five years Gennum has spent an average of 5% per annum of revenue to increase, upgrade and operate its computational, design and operational hardware and software.

Gennum's Quality Assurance group has a wide range of specialized and precision hardware. This ranges from automatic test equipment (ATE) for electrical tests, to scanning electron microscopes for visual analysis. Process and product qualifications use sophisticated reliability and failure analysis equipment.

#### **WORLD CLASS EXCELLENCE**

Gennum's benchmarks for excellence are the industry norms. Traditionally industry standards were set by the Japanese. However, with the introduction in 1988 of the Malcolm Baldridge National Quality Award in the U.S.A., a new vigour has developed in the West. This ensures that standards improve yet remain competitive.

The judging critieria for the Malcolm Baldrige National Quality Awards are sevenfold and summarize Gennum's focus and efforts:

#### 1. LEADERSHIP

It measures the success of senior management in creating and sustaining a quality culture.

#### 2. INFORMATION AND ANALYSIS

This measures the effectiveness of the company's collection and analysis of information for quality planning and improvement.

#### 3. PLANNING

Planning judges the effectiveness of integration of quality requirements into the company's business plans.

#### 4. HUMAN RESOURCE UTILIZATION

It measures the success of the company's efforts to utilize the full potential of the workforce for quality.

#### 5. QUALITY ASSURANCE

QA looks at the effectiveness of the company's systems for assuring quality control of all operations.

#### 6. QA RESULTS

QA evaluates the company's results in quality achievement and quality improvement, demonstrated through quantative measures.

#### 7. CUSTOMER SATISFACTION

It judges the effectiveness of the company's systems to determine customer requirements and demonstrated success in meeting those requirements.

#### QUALIFICATION

The purpose of qualification is to ensure that only reliable products will be introduced into the manufacturing stage, and ultimately reach the marketplace.

Two levels of qualification test routines are performed on all new product designs at Gennum

- Initial Qualification from

Design to Preproduction

- representative sample

- attribute tests

- high temperature storage

- temperature shocks

- attribute tests

- report

- 2. Follow-up Qualification from Preproduction to Production

- representative sample

- attribute tests

- high temperature burn-in

- temperature cycle

- attribute tests

- pressure cook/temperature humidity bias (95°C / 95%RH)

- attribute tests

- report

**Environmental Lab**

#### **CALIBRATION**

A calibration program has been established which covers all equipment used to design, manufacture, test and inspect products. This program is traceable to national standards and is performed inhouse by an independent service from outside the company.

#### **QUALITY LEVELS**

Quality means conformance to defined specifications and standards, through measureable and monitable parameters.

MIL.STD.38510 is used for general specifications of microelectronics.

At the output of Wafer Fabrications, and Assembly Operations, Quality Assurance gates have been established to ensure that in-line systems are effectively producing products which conform to specifications. Guidelines for Gennum quality inspection is MIL.STD.883C for test methods and procedures for microelectonics, and BR513, a 70 page Die Inspection Criteria document using method 2010, class B.

All finished devices are subject to both mechanical and electrical inspection based in MIL.STD.105D sampling plans. All outgoing inspection data is analyzed so as to monitor outgoing quality performance.

#### The Ultimate Goal: Zero Defects

Q.A. Station

# VIDEO & BROADCAST PRODUCTS

# Monolithic 1x1 Video Crosspoint Switch

GX401 DATA SHEET

#### **FEATURES**

- 100 MHz bandwidth (-3 dB)

- insertion loss 0.03dB at 100 kHz

- gain spread ±0.075dB at 8 MHz

- differential gain at 3.58 MHz 0.04% (max)

- differential phase at 3.58 MHz 0.02° (max)

- TTL and 5 V CMOS compatible logic inputs

- · compatible with all popular video standards

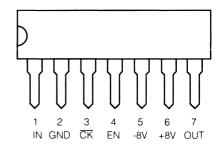

- 7 pin single-in-line package

- · built-in enable latch allows synchronous selection

#### CIRCUIT DESCRIPTION

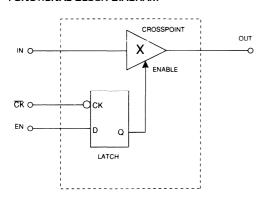

The GX401 is a low cost monolithic 1x1 video crosspoint switch plus on-board latch, designed primarily for use in video switching applications where 1 out of N channel selection function is required. Unlike similar devices using MOS bilateral switching elements, the GX401 represents a fully buffered unilateral transmission path when enabled, and offers better than 90 dB of off-isolation at 10 MHz when disabled.

In addition, the GX401 offers wide bandwidth and superior differential gain and phase performance.

Power supply requirements are ±8 volts. Logic inputs are TTL and 5V CMOS compatible.

#### **FUNCTIONAL BLOCK DIAGRAM**

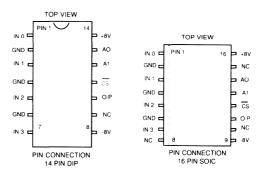

#### PIN CONFIGURATION

#### **ABSOLUTE MAXIMUM RATINGS**

| Parameter                            | Value                                                     |

|--------------------------------------|-----------------------------------------------------------|

| Supply Voltage                       | ± 10 0 V                                                  |

| Operating Temperature Range          | 0° C ≤ T <sub>A</sub> ≤ 70° C                             |

| Storage Temperature Range            | -65° C ≤ T <sub>S</sub> ≤ 150° C                          |

| Lead Temperature (Soldering, 10 Sec) | 260° C                                                    |

| Analog Input Voltage                 | $-4 \text{ V} \le \text{V}_{1\text{N}} \le 2.4 \text{ V}$ |

| Logic Input Voltage                  | $-4 \text{ V} \le \text{V}_{\text{L}} \le 5.25 \text{ V}$ |

NOTE: Output is not short circuit protected.

#### **ORDERING INFORMATION**

| Part Number | Package Type | Temperature Range |

|-------------|--------------|-------------------|

| GX401 CSN   | 7 Pin SIP    | 0° to 70°C        |

Document No. 510 - 9 - 4

2-1

## $\textbf{ELECTRICAL CHARACTERISTICS} \quad \text{(V}_{\text{S}} = \pm 8 \text{V DC.} \quad 0^{\circ}\text{C} < \text{T}_{\text{A}} < 70^{\circ}\text{C.} \text{ R}_{\text{L}} = 10 \text{k}\Omega. \text{ C}_{\text{L}} = 30 \text{pF. Typical values are at T}_{\text{A}} = 25^{\circ}\text{C)}$

|         | PARAMETER                       | SYMBOL                | CONDITIONS                                          | MIN  | TYP  | MAX    | UNITS   |

|---------|---------------------------------|-----------------------|-----------------------------------------------------|------|------|--------|---------|

|         | Supply Voltage                  | V <sub>S</sub> ±      |                                                     | 7.5  | 8.0  | 8.5    | ٧       |

| DC      |                                 | I+                    | Chip selected (EN=1)                                | -    | 15   | 18     | mA      |

| SUPPLY  |                                 |                       | Chip not selected (EN=0)                            | -    | 0.7  | 0.9    | mA      |

| į       | Supply Current                  | I-                    | Chip selected (EN=1)                                | -    | 14   | 17     | mA      |

|         |                                 |                       | Chip not selected (EN=0)                            | -    | 0.63 | 0.85   | mA      |

|         | Analog Output<br>Voltage Swing  | V <sub>OUT</sub>      | Extremes before clipping occurs                     | -1.2 | -    | +2.0   | ٧       |

| STATIC  | Output Offset Voltage           | V <sub>os</sub>       | 75Ω resistor on each input to gnd                   | 5    | 15   | 25     | mV      |

|         | Output Offset Voltage<br>Drift- | ΔV <sub>OS</sub> / ΔT |                                                     | -    | 50   | 200    | μV/°C   |

|         | Crosspoint<br>Turn-On Time      | ton                   | Control input to appearance of signal at output.    | 300  | 400  | 500    | ns      |

|         | Crosspoint<br>Turn-Off Time     | t <sub>OFF</sub>      | Control input to disappearance of signal at output. | 900  | 1200 | 1600   | ns      |

| i       | Clock input<br>Pulse width      | t <sub>CK</sub>       | Control input to appearance of signal at output.    | 350  | -    | -      | ns      |

| LOGIC   | Logic Input                     | V <sub>IH</sub>       | 1                                                   | 2.0  | -    | -      | V       |

|         | Thresholds                      | V <sub>IL</sub>       | 0                                                   | -    | -    | 0.8    | V       |

|         | Enable                          | I <sub>BIAS(EN)</sub> | EN = 1                                              | -    | -    | 2.0    | μА      |

|         | Bias Current                    |                       | EN = 0                                              | -    | -    | -0.1   | μА      |

|         | Insertion Loss                  | I.L.                  | 1V p-p sine or sq. wave at 100 kHz                  | 0.02 | 0.03 | 0.05   | dB      |

|         | Bandwidth (-3dB)                | B.W.                  |                                                     | 100  | -    | -      | MHz     |

|         | Gain Spread at 8 MHz            |                       |                                                     | -    | -    | ±0.075 | dB      |

|         | Input Resistance                | R <sub>IN</sub>       | Chip selected (EN = 1)                              | 900  | -    | -      | kΩ      |

| DYNAMIC | Input Capacitance               | C <sub>IN</sub>       | Chip selected (EN = 1)                              | -    | 2.0  | -      | ρF      |

|         |                                 |                       | Chip not selected (EN = 0)                          | -    | 2.2  | -      | ρF      |

|         | Output Resistance               | R <sub>out</sub>      | Chip selected (EN = 1)                              | -    | 12   | -      | Ω       |

|         | Output Capacitance              | Соит                  | Chip not selected (EN = 0)                          | -    | 7    | -      | pF      |

|         | Differential Gain               | dg                    | f = 3.58 or 4.43 MHz                                | -    | 0.03 | 0.04   | %       |

|         | Differential Phase              | dp                    | V <sub>IN</sub> = 40 IRE                            | -    | 0.01 | 0.02   | degrees |

|         | Off Isolation                   |                       | Crosspoint on output to gnd. $f = 10 \text{ MHz}$   | 90   | -    | -      | dB      |

**AVAILABLE PACKAGING**

7 pin SIP

CAUTION

ELECTROSTATIC

SENSITIVE DEVICES

DO NOT OPEN PACKAGES OR HANDLE

EXCEPT AT A STATIC FREE WORKSTATION

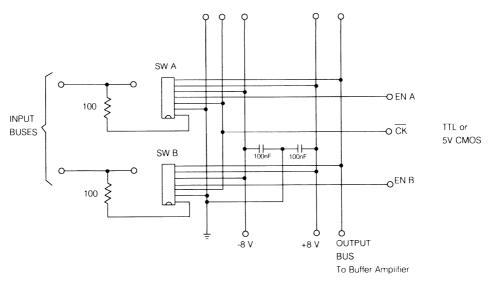

#### To other GX401s on same output bus

2-3

#### TYPICAL GX401 APPLICATION CIRCUIT

TYPICAL CROSSPOINT SELECTION TIMING DIAGRAM

# Monolithic 1x1 Video Crosspoint Switch with Two Latches

GX411 PRELIMINARY DATA SHEET

#### **FEATURES**

- \* differential gain at 3.58 MHz, 0.05% (max.)

- \* differential phase at 3.58 MHz, 0.025 deg.(max.)

- \* dual latches

- \* off-isolation at 10 MHz, 90 dB (min.)

- \* -3 dB bandwidth, 100 MHz (min.)

- \* insertion loss at 100 kHz, 0.03 dB (typ.)

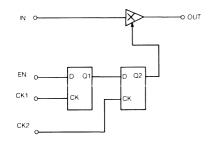

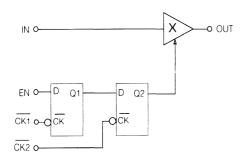

#### **FUNCTIONAL BLOCK DIAGRAM**

#### TRUTH TABLES

| EN | CK1 | CK2 | Q1                | Q2                |

|----|-----|-----|-------------------|-------------------|

| 0  | 1   | 0   | 0                 | Q2 <sub>n-1</sub> |

| 0  | 1   | 1   | 0                 | 0                 |

| 1  | 1   | 0   | 1                 | Q2 <sub>n-1</sub> |

| 1  | 1   | 1   | 1                 | 1                 |

| Х  | 0   | 0   | Q1 <sub>n-1</sub> | Q2 <sub>n-1</sub> |

| Х  | 0   | 1   | Q1 <sub>n-1</sub> | Q1 <sub>n-1</sub> |

X = DON'T CARE

| Q2 | ОUТ    |

|----|--------|

| 0  | HIGH Z |

| 1  | IN     |

#### CIRCUIT DESCRIPTION

The GX411 is a broadcast quality 1x1 video crosspoint featuring two control latches, implemented in bipolar monolithic technology. The device is characterized by low differential gain and phase, extremely high offisolation, and a -3 dB bandwidth of 100 MHz.

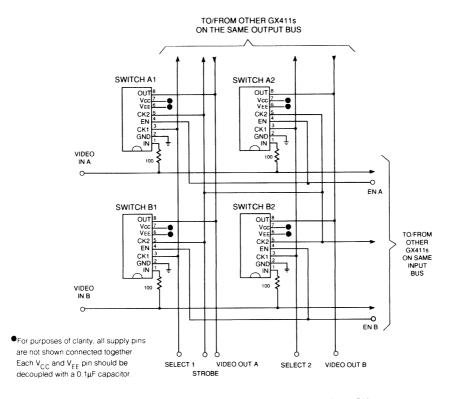

For use in NxM routing matrices, the GX411 features very high output impedance in the disabled state. This allows multiple devices to be paralleled at the input and output without additional circuitry. A fully buffered unilateral signal path ensures negligible output to input feedback while delivering minimal output switching transients through make-before-break switching.

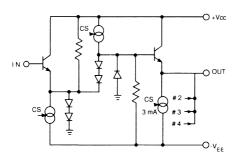

To maximize system bandwidth, an external current source is used to bias the output device of the crosspoint. One external current source is required per output bus. For less demanding applications, a load resistor can be used in place of the output current source, causing a slight increase in differential phase. Non-additive mixing will occur on the output bus if more than one paralleled GX411 is enabled at a time.

Dual transparent latches allow asynchronous addressing and synchronous switching. The control microprocessor can write to the input latch using *CK1*, while the video timing clock can be used to initiate switching using *CK2*. Alternatively, one or both of the latches can be made transparent by pulling *CK1* or *CK2* high.

The device operates over a supply voltage range from  $\pm 7$  to  $\pm 13.2$  volts. With a supply voltage of  $\pm 8$  V, the device dissipates only 8 mW in the disabled state.

#### **APPLICATIONS**

- video routing switchers

- video production and master control switchers

- CCTV / CATV

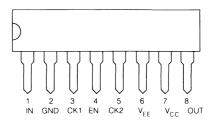

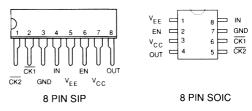

PIN CONNECTION 8 PIN SIP

#### **ORDERING INFORMATION**

| Part Number | Package   | Temperature Range |

|-------------|-----------|-------------------|

| GX411 CSA   | 8 pin SIP | 0°C to 70°C       |

Document No. 510 - 56

#### **ABSOLUTE MAXIMUM RATINGS**

| Parameter                   | Value                                                                  |

|-----------------------------|------------------------------------------------------------------------|

| Supply Voltage              | ± 13.5 V                                                               |

| Operating Temperature Range | $0  ^{\circ}\text{C} \le \text{T}_{\text{A}} \le 70  ^{\circ}\text{C}$ |

| Storage Temperature Range   | -65 °C ≤ T <sub>S</sub> ≤ 150 °C                                       |

| Parameter              |                                                                        | Value                          |

|------------------------|------------------------------------------------------------------------|--------------------------------|

| Lead Temperature (Sole | dering, 10 Sec)                                                        | 260 °C                         |

| Analog Input Voltage   | $-5 \text{ V} \leq \text{V}_{\text{IN}} \leq \text{V}_{\text{CC}} + 0$ | 0.3 V or V <sub>EE</sub> +20 V |

| Logic Input Voltage    |                                                                        | $0~V~\leq V_{L} \leq 5.5~V$    |

## ELECTRICAL CHARACTERISTICS ( $V_S = \pm 8 \text{ V DC}$ , $0^{\circ}\text{C} < T_A < 70 ^{\circ}\text{C}$ , $R_L = 10 \text{ k}\Omega$ , $C_L = 30 \text{pF}$ , $I_L = 2 \text{ mA}$ )

|         | PARAMETER                             | SYMBOL                | CONDITIONS                                       | MIN  | TYP  | MAX   | UNITS   |

|---------|---------------------------------------|-----------------------|--------------------------------------------------|------|------|-------|---------|

| DC -    | Supply Voltage                        | ± V <sub>S</sub>      |                                                  | 7    | 8    | 13.2  | V       |

| SUPPLY  |                                       | I +                   | Q2 = 1                                           | -    | 9.7  | 12.6  | mA      |

| SUPPLY  | Supply Current                        | 1+                    | Q2 = 0                                           | -    | 0.45 | 0.59  | mA      |

|         | (I <sub>1</sub> of 2 mA not included) | -1                    | Q2 = 1                                           | -    | 9.5  | 12.4  | mA      |

|         | (I <sub>L</sub> or 2 mA not included) |                       | Q2 = 0                                           | -    | 0.38 | 0.5   | mA      |

|         | Analog Output<br>Voltage Swing        | V <sub>OUT</sub>      | Extremes before clipping occurs                  | -2   | -    | 5.5   | V       |

| STATIC  | Analog Input Bias<br>Current          | I <sub>BIAS</sub>     |                                                  | -    | 20   | -     | μА      |

|         | Output Offset Voltage                 | V <sub>os</sub>       | T <sub>A</sub> = 25 °C                           | -10  | -    | 10    | mV      |

|         | O/P Offset Voltage Drift              | ΔV <sub>OS</sub> / ΔT |                                                  | -    | 50   | 200   | μV / °C |

|         | Crosspoint selection<br>Turn-on time  | t <sub>ore</sub>      | From CK2<br>From EN                              | -    | 0.7  | -     | μs      |

|         | Crosspoint selection Turn-off time    | t <sub>OFF</sub>      | From CK2<br>From EN                              |      | 2.2  | -     | μs      |

|         | Clock Pulse Width                     | t <sub>CK</sub>       |                                                  | 500  | -    | -     | ns      |

| LOGIC   | Logic Input                           | V <sub>IH</sub>       | 1                                                | 2.0  | -    | -     | V       |

|         | Thresholds                            | V <sub>IL</sub>       | 0                                                | -    | -    | 1.1   | V       |

|         | Enable Input<br>Bias Current          | I <sub>BIAS(EN)</sub> | EN=1                                             | -    | 0.5  | 3.0   | μА      |

|         | CK1/CK2 Bias Current                  | I <sub>BIAS(CK)</sub> | CK1/CK2=0                                        | -    | 0.7  | 5.0   | μА      |

|         | Insertion Loss                        | I.L.                  | 1V p-p sine or sq. wave<br>at 100 kHz            | 0.02 | 0.03 | 0.05  | dB      |

|         | Bandwidth (-3dB)                      | B.W.                  |                                                  | 100  | -    | -     | MHz     |

|         | Gain Spread at 8 MHz                  |                       |                                                  | -    | -    | ±0.06 | dB      |

|         | Input Resistance                      | R <sub>IN</sub>       | Chip selected                                    | 1    | -    | -     | МΩ      |

| DYNAMIC | Input Capacitance                     | C <sub>IN</sub>       |                                                  | -    | 2    | -     | pF      |

|         | Output Resistance                     | R <sub>OUT</sub>      |                                                  | -    | 15   | -     | Ω       |

|         | Output Capacitance                    | C <sub>OUT</sub>      |                                                  | -    | 3.5  | -     | pF      |

|         | Differential Gain                     | dg                    | at 3.58 MHz                                      | -    | -    | 0.05  | %       |

| -       | Differential Phase                    | dp                    | V <sub>IN</sub> = 40 IRE                         | -    | -    | 0.025 | deg.    |

|         | Off Isolation                         |                       | Crosspoint on output to gnd $f = 10 \text{ MHz}$ | 90   | 100  | -     | dB      |

| -       | Slew Rate                             | +SR                   | $V_{IN} = 3V p - p (C_L = 0 pF)$                 | 120  | 190  | -     | V/µs    |

|         |                                       | -SR                   |                                                  | 110  | 170  | -     |         |

Fig 1 Typical Application Circuit of Four GX411's Connected as a 2x2 Matrix.

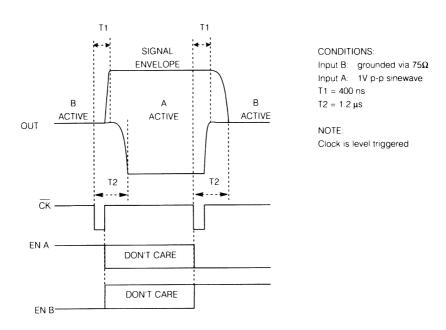

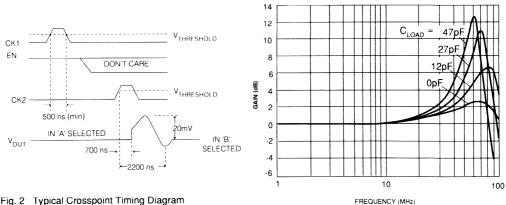

Fig. 2 Typical Crosspoint Timing Diagram

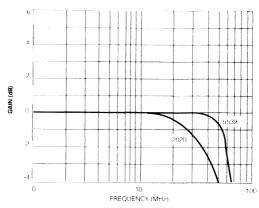

Fig. 3 Gain vs Frequency

### Wideband, Monolithic 1x1 Video Crosspoint Switch

#### GX4201 PRELIMINARY DATA SHEET

#### **FEATURES**

- \* -3 dB bandwidth, 300 MHz with C<sub>1</sub> = 0 pF

- \* off isolation at 100 MHz, 80 dB

- \* differential phase and gain at 4.43 MHz, 0.01° & 0.02%

- \* 600 µW disabled power consumption

- \* input signal levels from -2 V to +3 V

- \* logic input compatible with TTL and 5 V CMOS

- \* open collector TALLY output

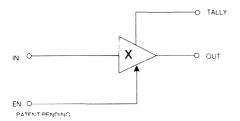

#### **FUNCTIONAL BLOCK DIAGRAM**

#### **TRUTH TABLE**

| EN | OUT    | TALLY |

|----|--------|-------|

| 0  | HIGH Z | OFF   |

| 1  | IN     | ON    |

#### **ABSOLUTE MAXIMUM RATINGS**

| Parameter                          | Value                                                             |

|------------------------------------|-------------------------------------------------------------------|

| Supply Voltage                     | ±7.5 V                                                            |

| Operating Temperature Range        | $0^{\circ} \text{ C} \leq \text{T}_{A} \leq 70^{\circ} \text{ C}$ |

| Storage Temperature Range          | -65° C ≤ T <sub>S</sub> ≤ 150° C                                  |

| Lead Temperature (Soldering, 10 Se | ec) 260° C                                                        |

| Analog Input Voltage               | $-5.5 \text{ V} \le \text{V}_{1\text{N}} \le 5.5 \text{ V}$       |

| Logic Input Voltage                | $-0.5 \text{ V} \le \text{V}_{\text{L}} \le 5.5 \text{ V}$        |

| Output Load Current                | 12mA                                                              |

| High Level TALLY Output Current    | 2 mA                                                              |

#### CIRCUIT DESCRIPTION

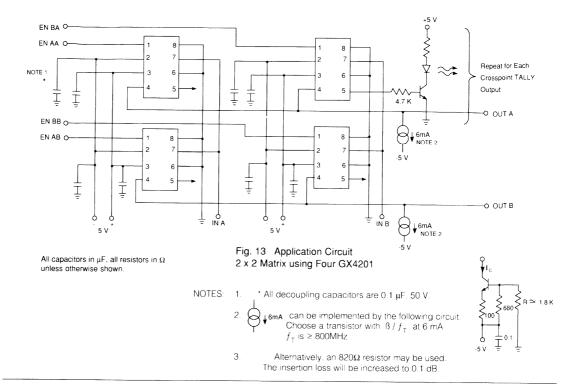

The GX4201 is a wideband 1x1 video crosspoint implemented in bipolar monolithic technology. The device is characterized by excellent differential gain and phase in the enabled state, and very high off-isolation in the disabled state. The fully buffered unilateral signal path ensures negligible output to input feedback while delivering minimal output switching transients through make-before-break switching.

For use in NxM routing matrices, the device features a very high, nearly constant input impedance, coupled with very high output impedance in the disabled state. This allows multiple GX4201's to be paralleled at the input and output without additional circuitry. An open collector PNP toV<sub>CC</sub>TALLY output provides indication of crosspoint selection.

To maximize system bandwidth, an external current source is used to bias the output device of the crosspoint. One external current source is required per output bus. For less demanding applications, a load resistor can be used in place of the output current source, causing a slight increase in differential phase. Non-additive mixing will occur on the output bus if more than one paralleled GX4201 is enabled at a time.

The GX4201 is one of a series of wideband video cross-points utilizing Gennum's proprietary LSI process.

#### **APPLICATIONS**

- \* very high quality video switching

- \* HDTV

- \* computer graphics

- \* RF switching/routing

- \* PCM/data routing

#### PIN CONNECTIONS

Document No. 510 - 74 - 3

## **ELECTRICAL CHARACTERISTICS** $(V_S = \pm 5 \text{V DC}, 0 \text{°C} < T_A < 70 \text{°C}, I_L = 6 \text{ mA})$

|         | PARAMETER                        | SYMBOL                | CONDITIONS                                                                            | MIN  | TYP   | MAX  | UNITS   |

|---------|----------------------------------|-----------------------|---------------------------------------------------------------------------------------|------|-------|------|---------|

|         | Supply Voltage                   | ±V <sub>S</sub>       |                                                                                       | ±4.5 | ±5    | ±5.5 | V       |

| DC      |                                  | I +                   | EN=1                                                                                  | -    | 12    | 15.6 | mA      |

| SUPPLY  | Supply Current                   |                       | EN=0                                                                                  | -    | 50    | 100  | μА      |

|         | (not including external          | I-                    | EN=1                                                                                  | -    | 11    | 14.3 | mA      |

|         | current load)                    |                       | EN=0                                                                                  | -    | 70    | 140  | μА      |

|         | Analog Output<br>Voltage Swing   | V <sub>OUT</sub>      | Extremes before clipping occurs                                                       | -2   | -     | 3    | ٧       |

| STATIC  | Analog Input Bias<br>Current     | I <sub>BIAS</sub>     |                                                                                       | -    | 12    | -    | μА      |

|         | Output Offset Voltage            | V <sub>OS</sub>       | T <sub>A</sub> = 25°C                                                                 | -10  | -     | 10   | mV      |

|         | Output Offset Voltage<br>Drift-  | ΔV <sub>os</sub> / ΔT |                                                                                       | -    | -25   | -80  | μV/°C   |

|         | Crosspoint<br>Turn-On Time       | <sup>t</sup> on       | Control input to appearance of signal at output.                                      | -    | 200   | 400  | ns      |

| LOGIC   | Crosspoint<br>Turn-Off Time      | t <sub>OFF</sub>      | Control input to disappearance of signal at output.                                   | 0.5  | 1.0   | -    | μs      |

|         | Logic Input                      | V <sub>IH</sub>       | 1                                                                                     | 2.0  | -     | -    | ٧       |

|         | Thresholds                       | V <sub>IL</sub>       | 0                                                                                     | -    | -     | 0.8  | ٧       |

|         | Enable<br>Bias Current           | BIAS(EN)              | EN = 0                                                                                | -    | -     | 2    | μА      |

|         | TALLY Output                     | V <sub>OH</sub>       | EN = 1. I <sub>O</sub> = 1mA                                                          | 4.80 | 4.89  | 4.92 | ٧       |

|         | Insertion Loss                   | I.L.                  | 1V p-p sine or sq. wave<br>at 100 kHz R <sub>I</sub> =10K, C <sub>I</sub> =30pF       | -    | 0.025 | _    | dB      |

|         | Bandwidth (-3dB)<br>See Fig. 1   | B.W.                  | small signal C <sub>L</sub> = 0 pF                                                    | -    | 300   | -    | MHz     |

|         | Input Resistance                 | R <sub>IN</sub>       | EN = 1                                                                                | 1.0  | 3.0   | -    | МΩ      |

| DYNAMIC | Input Capacitance                | C <sub>IN</sub>       | EN = 0                                                                                | -    | 1.1   |      | pF      |

|         | Output Resistance                | R <sub>OUT</sub>      | EN = 1                                                                                | -    | 7     | -    | Ω       |

|         | Output Capacitance<br>See Fig. 5 | C <sub>OUT</sub>      | EN = 0                                                                                | =    | 1.1   | -    | pF      |

|         | Differential Gain                | dg                    | at 3.58 MHz                                                                           | -    | -     | 0.04 | %       |

|         | Differential Phase<br>See Fig. 6 | dp                    | V <sub>IN</sub> = 40 IRE                                                              | -    | -     | 0.04 | degrees |

|         | Off Isolation<br>See Fig. 4      |                       | Enabled GX4201 on output $f = 100 \text{ MHz}  \text{V}_{\text{IN}} = 1 \text{V p-p}$ | •    | 80    | -    | dB      |

|         | Slew Rate                        | +SR                   | TIV.                                                                                  | 250  | 400   | -    |         |

|         |                                  | -SR                   | $V_{IN} = 3V p-p (C_L = 0 pF)$                                                        | 250  | 350   | -    | V/µs    |

#### **ORDERING INFORMATION**

| PART NUMBER  | PACKAGE TYPE | TEMPERATURE RANGE |

|--------------|--------------|-------------------|

| GX4201 - CKA | 8 PIN SOIC   | 0° to 70°C        |

| GX4201 - CDA | 8 PIN DIP    | 0° to 70°C        |

CAUTION

ELECTROSTATIC

SENSITIVE DEVICES

DO NOT OPEN PACKAGES OR HANDLE

EXCEPT AT A STATIC-FREE WORKSTATION

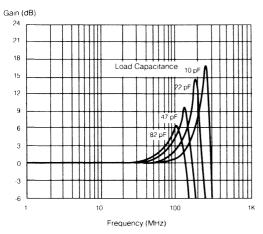

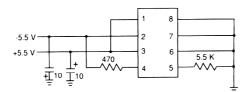

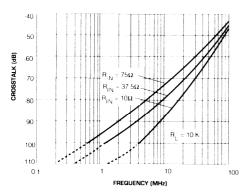

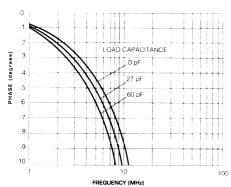

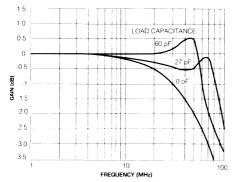

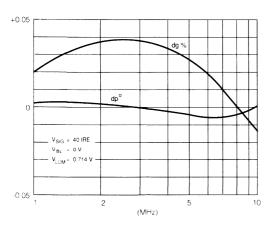

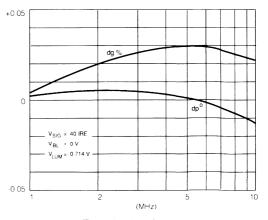

#### TYPICAL PERFORMANCE CURVES OF THE GX4201

For all graphs,  $V_S = \pm 5$  V DC and  $T_A = 25$ °C. The curves shown below represent typical batch sampled results.

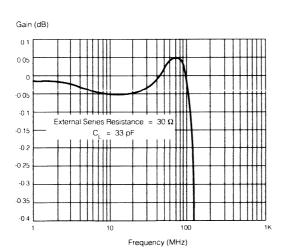

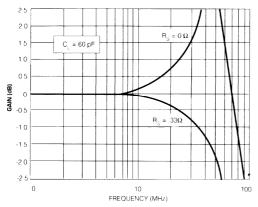

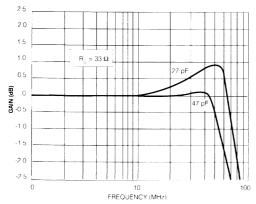

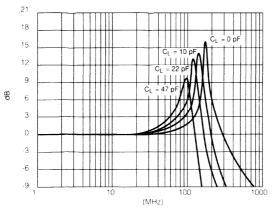

Fig. 1 Gain vs Frequency

Fig. 3 Gain vs Frequency

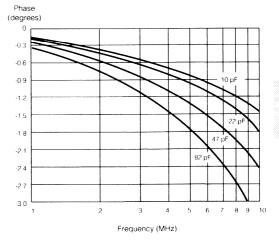

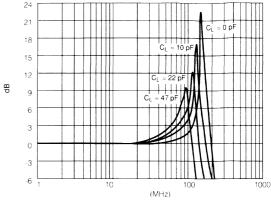

Fig. 2 Phase vs Frequency

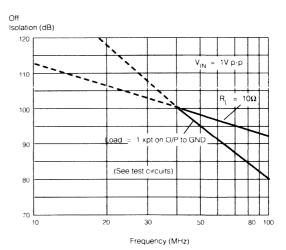

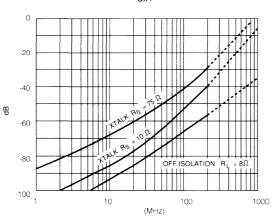

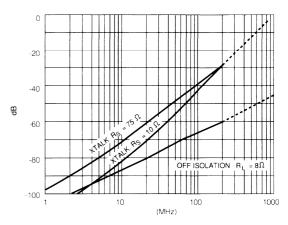

Fig. 4 Off Isolation vs Frequency

continued over

2-11

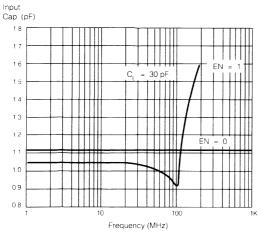

Fig. 5 C<sub>IN</sub> vs Frequency

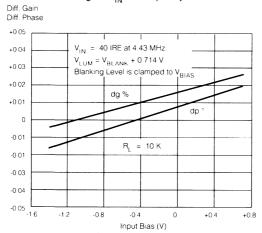

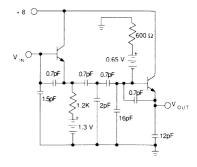

Fig. 7 dg/dp vs Input Bias

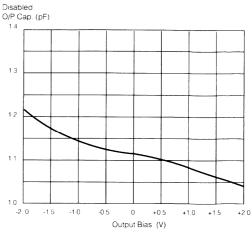

Fig. 6  $\,{\rm C}_{\rm OUT}^{}\,{\rm vs}$  Bias

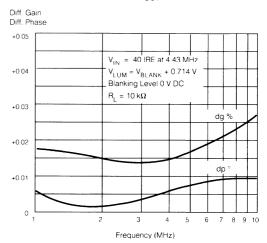

Fig. 8 dg/dp vs Frequency

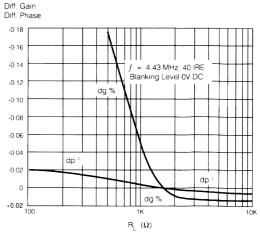

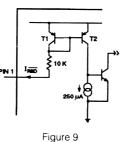

Fig. 9 dg/dp vs R

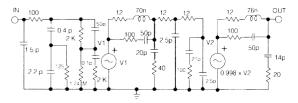

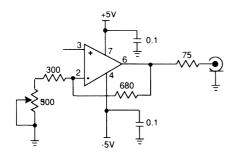

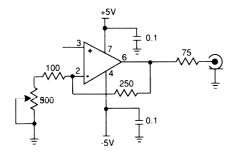

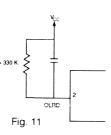

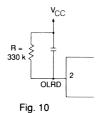

Fig. 10 Burn-in Test Circuit

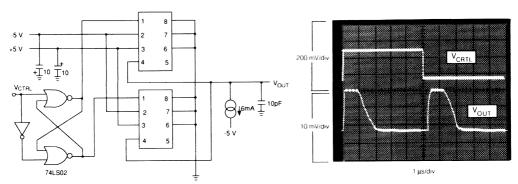

Fig. 11a Switching Transient Test Circuit

Fig. 11b Switching Transient

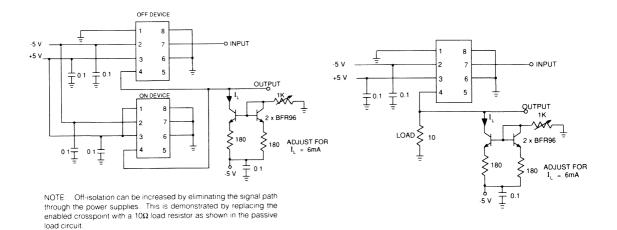

Active Load

Fig. 12 Off-isolation Test Circuits

Passive Load

# Wideband, Monolithic 1x1 Video Crosspoint Switch

GX4301 TENTATIVE DATA SHEET

## **FEATURES**

- -3 dB bandwidth, 300 MHz with C<sub>1</sub> = 0 pF

- . off isolation at 100 MHz, 80 dB

- differential phase and gain at subcarrier 0.01° & 0.01%

- 1.65 mW disabled power consumption (± 5V Supplies)

- input signal levels from -2 V to +3 V (± 5V Supplies)

- dual, transparent control latches

- ± 5V to ± 12V supply voltage range

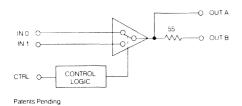

## **FUNCTIONAL BLOCK DIAGRAM**

### TRUTH TABLE

|                      | EN | CK1 | CK2 |    | Q1                | Q2                | Q2      | OUT    |

|----------------------|----|-----|-----|----|-------------------|-------------------|---------|--------|

|                      | 0  | 0   | 1   |    | 0                 | Q2 <sub>n-1</sub> | 0       | HIGH Z |

| Contract of the last | 0  | 0   | 0   |    | 0                 | 0                 | 1       | IN     |

|                      | 1  | 0   | 1   |    | 1                 | Q2 <sub>n-1</sub> |         |        |

|                      | 1  | 0   | 0   | ١. | 1                 | 1                 |         |        |

|                      | Х  | 1   | 1   |    | Q1 <sub>n-1</sub> | Q2 <sub>n-1</sub> | X = DON | CARE . |

|                      | Х  | 1   | 0   |    | Q1 <sub>n-1</sub> | Q1 <sub>n-1</sub> |         |        |

|                      |    |     |     |    |                   |                   |         |        |

## CIRCUIT DESCRIPTION

The GX4301 is a wideband 1x1 video crosspoint implemented in bipolar monolithic technology. The device is characterized by excellent differential gain and phase in the enabled state, and very high off-isolation in the disabled state. The fully buffered unilateral signal path ensures negligible output to input feedback while delivering minimal output switching transients through make-beforebreak switching.

For use in NxM routing matrices, the device features a very high, nearly constant input impedance, coupled with very high output impedance in the disabled state. This allows multiple GX4301's to be paralleled at the input and output without additional circuitry.

To maximize system bandwidth, an external current source is used to bias the output device of the crosspoint. One external current source is required per output bus. For less demanding applications, a load resistor can be used in place of the output current source, causing a slight increase in differential phase. Non-additive mixing will occur on the output bus if more than one paralleled GX4301 is enabled at a time.

Dual transparent latches allow asynchronous addressing and synchronous switching. The control microprocessor can write to the input latch using  $\overline{CK1}$ , while the video timing clock can be used to initiate switching using  $\overline{CK2}$ . Alternatively, one or both of the latches can be made transparent by pulling  $\overline{CK1}$  or  $\overline{CK2}$  low.

The GX4301 is one of a series of wideband video cross-points utilizing Gennum's proprietary LSI process.

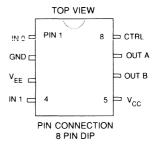

## **APPLICATIONS**

- \* very high quality video switching

- \* HDTV switching and routing

- \* computer graphics

- \* RF switching/routing

- \* PCM/data routing

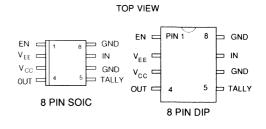

### PIN CONNECTIONS

Document No. 510 - 94

2-15

# $\textbf{ELECTRICAL CHARACTERISTICS} \ \, (\text{V}_{\text{S}} = \pm 8 \text{V DC} \quad 0^{\circ}\text{C} < \text{T}_{\text{A}} < 70^{\circ}\text{C}, \ \text{R}_{\text{L}} = 10 \ \text{k}\Omega, \ \text{C}_{\text{L}} = 30 \text{pF}, \ \text{I}_{\text{L}} = 6 \text{mA})$

|         | PARAMETER                            | SYMBOL                | CONDITIONS                                         | MIN | TYP        | MAX  | UNITS    |

|---------|--------------------------------------|-----------------------|----------------------------------------------------|-----|------------|------|----------|

|         | Supply Voltage                       | ±V <sub>S</sub>       |                                                    | 4.5 | -          | 13.2 | V        |

| DC      |                                      | I+                    | Q2=1                                               | -   | 11         | -    | mA       |

| SUPPLY  | Supply Current                       |                       | Q2=0                                               | -   | 200        | -    | μА       |

|         | (I <sub>L</sub> of 6mA not included) | I-                    | Q2=1                                               | -   | 10         | -    | mA       |

|         |                                      |                       | Q2=0                                               | -   | 130        | -    | μА       |

|         | Analog Output<br>Voltage Swing       | V <sub>OUT</sub>      | Extremes before clipping occurs                    | -2  | _          | 3    | V        |

| STATIC  | Analog Input Bias<br>Current         | I <sub>BIAS</sub>     |                                                    | -   | 12         | -    | μА       |

|         | Output Offset Voltage                | Vos                   | T <sub>A</sub> = 25°C                              | -10 | -          | 10   | mV       |

|         | Output Offset Voltage<br>Drift-      | ΔV <sub>OS</sub> / ΔT |                                                    | -   | -          | 100  | μV/°C    |

|         | Crosspoint selection                 | t <sub>on</sub>       | From CK2                                           | -   | 0.6        | -    | μs       |

|         | Turn-On Time                         |                       | From EN.                                           | -   | 0.8        |      | μs       |

| LOGIC   | Crosspoint selection Turn-Off Time   | t <sub>OFF</sub>      | From CK2 From EN                                   | -   | 2.0        | -    | μs<br>μs |

|         | Clock Pulse Width                    | t <sub>OFF</sub>      |                                                    | 500 |            |      | ns       |

|         | Logic Input                          | V <sub>IH</sub>       | 1                                                  | 2.0 | -          | _    | V        |

|         | Thresholds                           | V <sub>IL</sub>       | 0                                                  | -   | <b>†</b> . | 0.8  | V        |

| â       | Enable Input<br>Bias Current         | BIAS(EN)              | EN = 1                                             | -   | 0.1        | -    | μА       |

|         | CK1/CK2 Bias Current                 | BIAS(CK)              | CK = 1                                             | -   | 0.1        | -    | μА       |

|         | Insertion Loss                       | I.L.                  | 1V p-p sine or sq. wave at 100 kHz                 | -   | 0.025      | -    | dB       |

|         | Bandwidth (-3dB)                     | B.W.                  |                                                    | -   | 300        | -    | MHz      |

|         | Gain Spread at 30 MHz                |                       |                                                    | -   | -          | ±0.1 | dB       |

| ĺ       | Input Resistance                     | R <sub>IN</sub>       | Chip Selected                                      | 1   | -          | -    | МΩ       |

| DYNAMIC | Input Capacitance                    | CIN                   |                                                    | -   | 1.1        | -    | ρF       |

|         | Output Resistance                    | R <sub>OUT</sub>      |                                                    | -   | 7          | -    | Ω        |

|         | Output Capacitance                   | C <sub>OUT</sub>      |                                                    | -   | 1.1        | -    | pF       |

|         | Differential Gain                    | dg                    | at 3.58 MHz or 4 43 MHz                            | -   | 0.01       | -    | %        |

|         | Differential Phase                   | dp                    | V <sub>IN</sub> = 40 IRE                           | -   | 0.01       | -    | degrees  |

|         | Off Isolation                        |                       | Crosspoint on output to gnd. $f = 100 \text{ MHz}$ | -   | 80         | 100  | dB       |

|         | Siew Rate                            | +SR                   |                                                    | 250 | 400        | -    |          |

|         |                                      | -SR                   | $V_{IN} = 3V p-p (C_{L} = 0 pF)$                   | 250 | 350        | -    | V/µs     |

# ABSOLUTE MAXIMUM RATINGS

| Parameter                                   | Value                                                    |

|---------------------------------------------|----------------------------------------------------------|

| Supply Voltage                              | ±13.2 V                                                  |

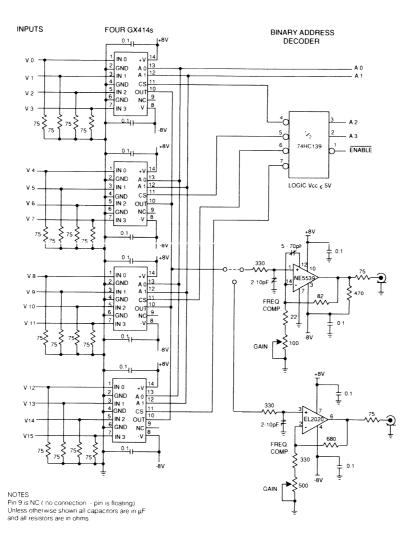

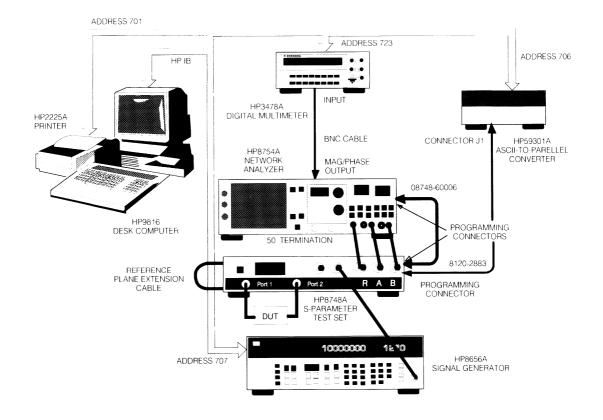

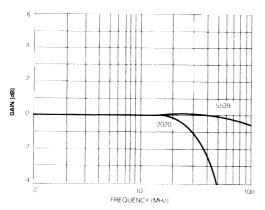

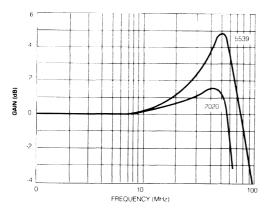

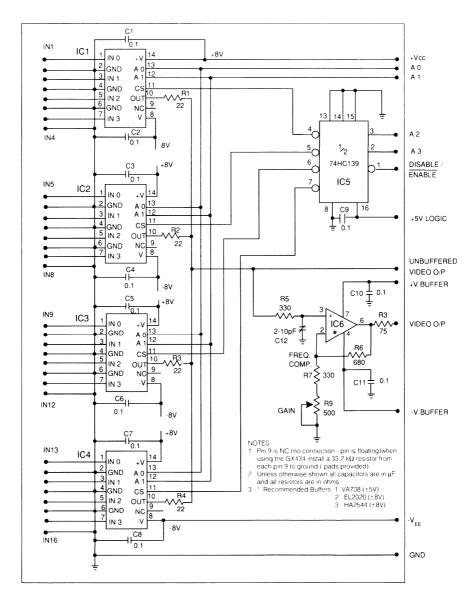

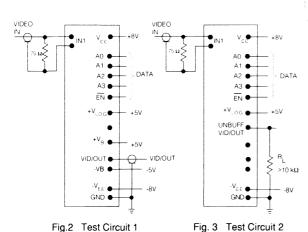

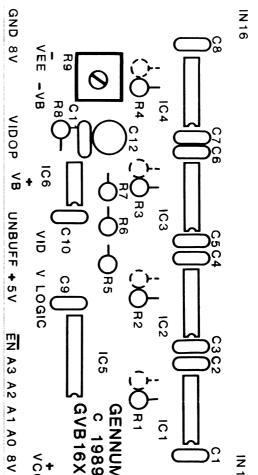

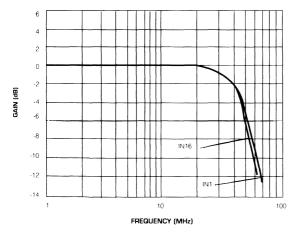

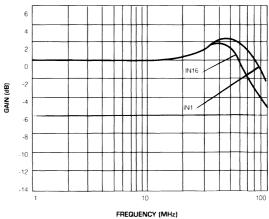

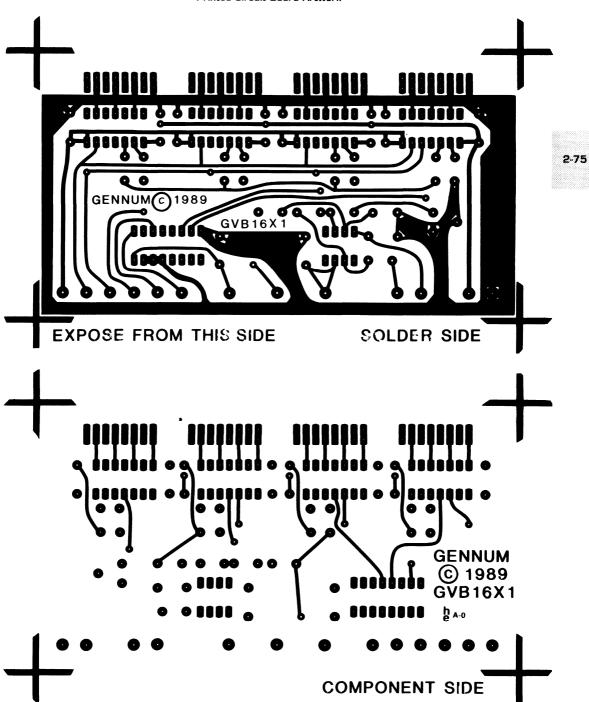

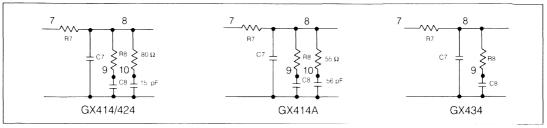

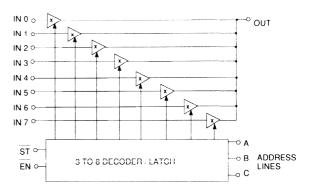

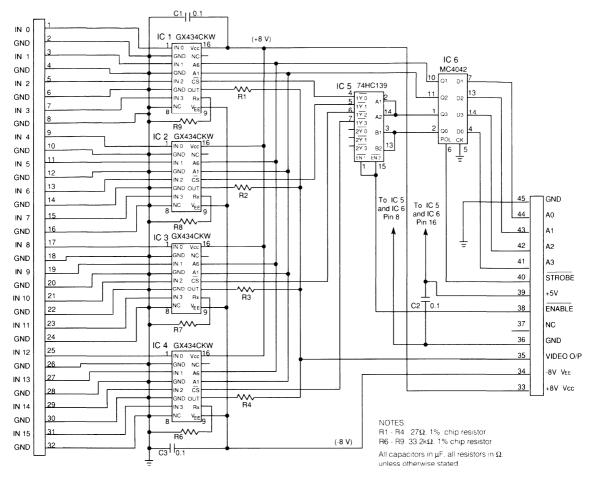

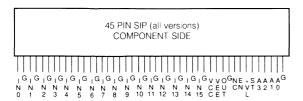

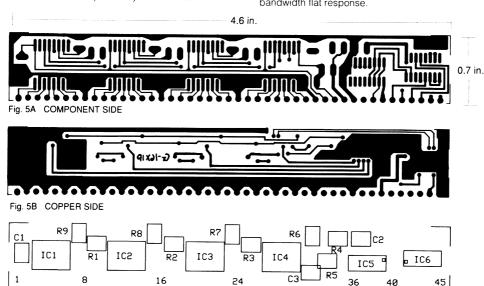

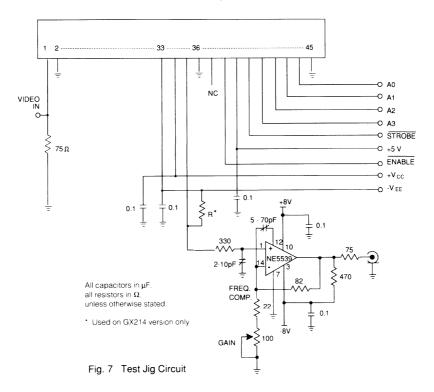

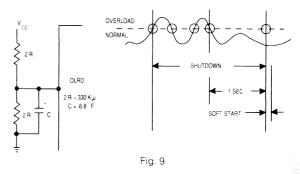

| Operating Temperature Range                 | 0° C ≤ T <sub>A</sub> ≤ 70° C                            |